最近人工智能芯片很火,华为发布了两款AI芯片—升腾910和310,阿里成立的芯片公司“平头哥”,首款AI芯片最快明年下半年面世,人工智能依然是风口。行业的另一个热点是RISC-V,65家机构发起成立了中国RISC-V产业联盟。那么,RISC-V的开源架构可以给人工智能芯片带来什么机遇呢?

RISC-V的首席构架师Krste Asanovic告诉我们:“Mi-V生态系统和PolarFire可为功率受限的嵌入式系统提供深度学习解决方案。”

Mi-V RISC-V生态系统开发平台是美高森美(Microsemi)加速生态系统计划的一部分,聚集了许多参与RISC-V开发的行业领导者,为客户充分利用其功能并简化RISC-V设计。Mi-V生态系统为固件和硬件工程师提供了全面的生态系统,让第三方能够使用这个平台推动RISC-V采用和创新。

在最近SiFive举办的RISC-V中国巡回研讨会上,Krste Asanovic博士向我们讲述了人工智能的进化史以及RISC-V给人工智能芯片所带来的机遇。

一、人工智能的三波浪潮

人工智能(Artificial Intelligence)始于人工神经网络。人工神经网络经历了三波浪潮:第一波是上世纪五十年代和六十年代,人类发明了感知器(模拟人类视神经控制系统的图形识别机);第二波是上世纪八十年代和九十年代,称为“反向传播”的浪潮;第三波浪潮是自2010年以来的深度神经网络。值得注意的是,所有开发出来的理念比实际最终流行都要早很多年。

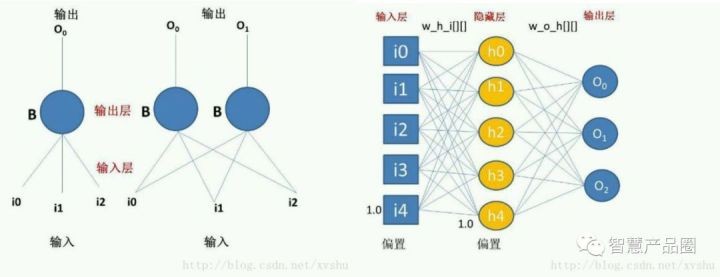

在上世纪五十年代和六十年代,人们发明了单层感知器。这个感知器最早是为图像处理开发的单层感知器(例如Rosenblatt),它只是一个“线性可分分类器”,不能捕获有趣函数,例如XOR函数。到了七十和八十年代,AI逐渐从统计方法转移到符号方法。

图一、人工神经网络单层/多层感知器

(来源:网络)

到了1986年,有影响力的PDP书籍出版,从单层感知器发展到了多层感知器与反向支撑。人们发现两层方向支撑训练网络在实现许多艰巨任务时明显好很多,但专家们一个广泛的抱怨是结果不可解释,而且用通用计算机训练的过程太慢了,所以要赶快建立定制机器。

这样就有了定制神经计算机。大的定制神经网络计算机的努力主要发生在九十年代。在上世纪九十年代逐渐有了DSP 阵列、矢量处理器、脉动阵列(Systolic arrays),以及其他更多的仿神经方法,例如:具有EEPROM权重的模拟、位系列技术、尖峰方法、异步处理器等等。

这里特别要提出的是1989年发明的环形阵列处理器(ICSI 1989),发明人是Nelson Morgan, Jim Beck, Phil Kohn, Jeff Bilmes。这是为快速训练建立的号称为“大转储”神经网络的RAP机,开辟了语音识别领域;九十年代美国德州仪器公司的环形浮点DSPs TMS320C30问世,每个DSP提供32MFLOPS(32-bit FP),每个板子上有4个DSP,10个电路板连接在一起(大于1GFLOP/s峰值,640MB DRAM)。其神经网格训练率大于100MCUPS(每秒百万级的链接升级),全部加起来有10个电路板。FPGA环连接用来为所有脉动阵列-即在训练和推理时的所有通讯,其快速、灵活的设计使其成为当时人工智能领域的一个“明星”,但是价格昂贵,每个电路板达10万美金。

二、专用和通用计算机之争

矢量微处理器(例如:Crays)在科学计算领域非常成功,它是一种全新的编程模型。给一个标准的MIPS RISC 标量处理器增加一个矢量协处理器,并全部集成在一个芯片,可用于神经网络训练。

第一台矢量微处理器是SPERT-II/T0,它产生于1995年。其系统被9个国际网站采用,作为人工智能的研发平台整整工作了9年,2004年它在最后一次“上班”后黯然下岗。

1997年出现了TetraSpert,它是一台可快速训练的矢量微处理器,使用SPARC工作站,通过Sbus总线连接若干台(4台)SRAM T0,进行神经网络的快速训练。西门子在1992年5月推出了SYNAPSE-1,这是一台“脉动阵列-多重引擎(16b*16b)”的处理器,可实现四级程序控制(68000s+微码)。

这个时代的人工智能处理器是“用简化的矢量处理填充掩模版,添加高宽带本地存储器,并向服务器附加多个以加速神经网络训练。”

九十年代的人工智能市场特点一个是很小,一个是神经网络开始“人气消退”,只有一小部分人还在坚持做这个,因为摩尔定律的微缩理论更看好通用型处理器。

1996年,Intel发布了奔腾MMX(Pentium MMX),从多能奔腾开始,英特尔就对其生产的CPU开始锁倍频了,但是MMX的CPU超外频能力特别强,而且还可以通过提高核心电压来超倍频,所以那个时候超频是一个很时髦的行动。

MIT计算机科学实验室的Krste Asanovic 发表了一篇论文“可编程神经计算方法”,文章说: “尽管迄今为止实现的多媒体扩展证实了基于定点矩阵码的通用微处理器有一个有限的提升,他们预示着商业微处理器制造商的意图是这种编码工作的很好,由于商业设计团队在新的微处理器设计中加入了多媒体内核的工作量,我们期待ANN算法的功能也能够大大增加,连续大量的投资都瞄准了高容量微处理器,以确保这些器件能使用最先进的制造工艺和更激进能够产生更高快速时钟速率的电路设计风格。在这种趋势下,势必减少了对于未来专用的神经计算机的兴趣。”

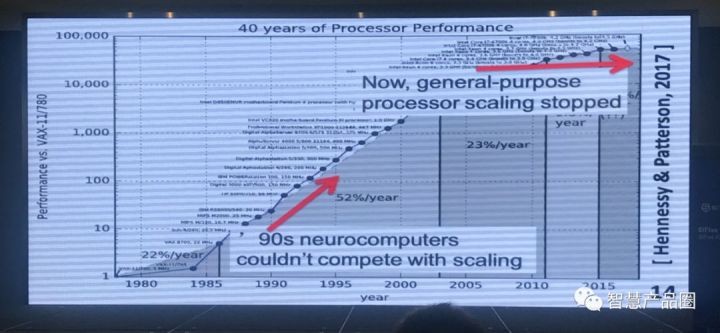

另外,随着年代,微处理器的功能提高速率在减慢:

1980~1985: 提升22%/年;

1985~2003: 提升52%/年;

2003~2011: 23%/年;

2011~2015: 9.3%/年;

2015年以后:2.3%/年。

图二、微处理器功能演进的40年

(数据来源:Hennessy & Patterson, 2017)

“现在的微处理器功能已经相当于将近10万个VAX-11/780工作站,进步惊人,但提升速率在下降,” Krste Asanovic博士说。“九十年代开始神经计算机已不能和微缩的通用计算机进行竞争了,但现在通用微处理器的工艺微缩停止了。”

三、图像处理器(GPU)

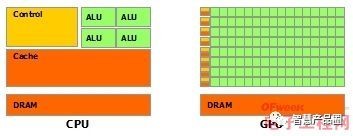

GPU和CPU之所以大不相同,是由于其设计目标的不同,它们分别针对了两种不同的应用场景。CPU需要很强的通用性来处理各种不同的数据类型,同时又要逻辑判断又会引入大量的分支跳转和中断的处理。这些都使得CPU的内部结构异常复杂。而GPU面对的则是类型高度统一的、相互无依赖的大规模数据和不需要被打断的纯净的计算环境。

图像处理器是在90年代中后期出现的,GPU的主要功能是产生3D图像,包括高端的浮点单元,提供工作站—像PC的图形,配置图形管道等,但在初期它并不能真正的进行编程。

进入21世纪以后,特别是2001年到2005年之间,随着时间的推移图像处理器加入了更多的可编程性能。例如,用来写小程序的新语言Cg在每个格点或每个像素进行,也在Windows DirectX变体上进行。出现了大量并行的(每框约上百万的格点或像素)但是非常严格的编程模型,某些用户注意到它也可以做通用计算,将输入输出数据映射到图像,计算格点和像素阴影。这些难以置信的编程模型,必须使用图像管道模型进行通用计算。

通用图像处理器(GP-GPU)的里程碑是2006年英伟达发布的GeForce 8800GPU,它可以支持一个新的可编程语言:CUDA,这是一个“统一计算设备架构”。接着,行业更广泛地推动了一个有同样想法的中立供应商版本OpenCL,其想法是,利用GPU的计算性能和存储器带宽来加速某些内核通用计算性能。这样就产生了附加处理器模型:主机CPU将数据并行内核发布到GPU执行,时间久了,就演变成为了速度最快的执行神经网络训练的标准方式。

图三、CPU和GPU的架构示意

(图片来自nVidia CUDA文档。其中绿色的是计算单元,橙红色的是存储单元,橙黄色的是控制单元)

此时GPU已经不再局限于3D图形处理了,GPU通用计算技术发展引起业界的关注,事实也证明在浮点运算、并行计算等部分计算方面,GPU可以提供数十倍乃至于上百倍于CPU的性能。

GPU采用了数量众多的计算单元和超长的流水线,但只有非常简单的控制逻辑并省去了Cache。而CPU不仅被Cache占据了大量空间,而且还有有复杂的控制逻辑和诸多优化电路,相比之下计算能力只是CPU很小的一部分。

所以与CPU擅长逻辑控制和通用类型数据运算不同,GPU擅长的是大规模并发计算(Concurrent computing),这也正是人工智能等所需要的。所以GPU除了图像处理,也越来越多的参与到计算当中来。

四、定制AI芯片的广泛努力

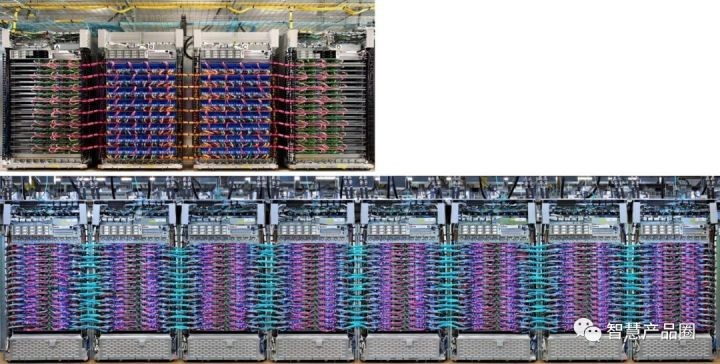

在图像处理器GPU逐渐演变为通用计算处理器的时候,许多定制芯片厂商也在努力开发定制AI芯片。例如Google推出的TPU(张量处理器)、TPUv2、TPUv3等云计算系列芯片,也有人称之为AI协同处理器。TPU的性能比现代CPU和GPU高15-30倍,每瓦性能提高30-80倍。

AI 加速器设计的原型是边缘推理(Inference at edge),它最关切的因素是成本、性能和功耗,需要高压缩的模块来减少系统成本和功耗,以及成本性能绩效。

云端推理最关切的是(交互)延迟、吞吐量和成本,响应用户要求的快速性和可预见力,因为有许许多多的用户,因此降低每个用户的成本是关键。

云端训练关切的是性能。价值是得出的数据模型,要为高的成本/功耗辩解。单次训练可达数周,优化技能人才开发稀缺资源。这个更像传统的HPC,而不像传统的云,追求极限的工艺,最先进的工艺节点,互连、冷却技术等等。

总的来说,云AI加速器的共性包括,专用矩阵引擎、压缩的定点/浮点格式、多片片上暂存存储器、先进节点中的全掩模板、最高带宽的外部DRAM、最高带宽的串行链路等。

假设以上条件全部成立,AI能够成功吗?Krste Asanovic博士给出了三点预测:第一、算法变化很快但模式经久;第二、摩尔定律死了但阿姆达尔定律(Amdahl’s Law)还活着;第三、软件最重要,但你永远无法完成它。阿姆达尔定律表明,即使到了多核时代,并发程序的开发或者说提升程序的并发度仍然具有十分重要的意义。

阿姆达尔定律是一个计算机科学界的经验法则,可用于指导CPU的可扩展设计。阿姆达尔定律指出,CPU的发展有两个方向,更快的CPU或者更多的核。目前看来发展的重心偏向了CPU的核数。但有时我们会发现虽然拥有更多的核,当我们同时运行几个程序时,只有少数几个线程处于工作中,其它的并未做什么工作,实践当中,并行运行多个线程往往并不能显著提升性能,程序往往并不能有效的利用多核,在多核处理器中加速比是衡量并行程序性能的一个重要参数。

AI的算法在流片和布局中一直在改变,按照伯克利的观点:“Dwarfs侏儒”是任何计算问题的最基本因素。Krste Asanovic博士说,“我不知道AI算法的未来是什么样子,但是他们将使用这些模式,设计永远是这些模式的灵活组合。”

摩尔定律死了,阿姆达尔定律活着,而且是活蹦乱跳地活着。

图四、谷歌推出的TPUv2(上)和 TPUv3(下)pod(来源:网络)

五、应用于AI加速器的RISC-V

软件被定义为通过优化算法训练的神经网络构架以解决特定的任务。今天,神经网络是用来学习解决问题的实际工具,其中涉及通过大数据集进行分类学习。

做研发的人有深切的体会,“在流片前永远结束不了软件工作,在流片前不太可能完成1%的软件工作,倾向于只编码了内核(1%)还剩99%,但你要记着阿姆达尔定律!”Krste Asanovic博士强调,“如果系统很难编程,那么就不会有软件了;如果你没有软件,你就不会有一个加速器!”

RISC-V是免费且开放的ISA,通过开放标准协作推动实现处理器创新的全新时代。RISC-V也可成为定制加速器的设计基础。

应用一个简单的基础ISA对所有核可以大大简化软件。例如,在你需要一个高性能Unix兼容核去运行操作系统时,建立一个超标量体系结构OoO核;在你微代码调度需要VLIW的时候,按顺序构建超标体系结构;在你需要低精度SIMD的地方,使用标准矢量扩展;在你想需要利用2D优化的地方(例如:多路脉动阵列、卷积),使用2D扩展(正在进行中);在你需要中断/响应I/O管理核的地方,建立嵌入式核;以及相同的存储器模块,同步基元,编程工具流程(C-结构包),查错,跟踪……等等。

RISC-V可定制化核有许多丰富的选择,包括被连接到相干高宽带结构的核和即将到来的矢量扩展、客户自定义指令扩展、依附在相干构造上的AI加速器等。

一个好消息是开源的Nvidia NVDLA 在其SiFive流行芯片上已经得到演示,SiFive Design Sharer提供了简洁全面的ASIC设计服务,以及提供应用于高宽带存储系统的HBM2 IP 和应用于柔性芯片连接的Interlaken IP等众多人工智能RISC-V IP核。