8月21日-23日,2024 RISC-V中国峰会主会圆满落幕。本届峰会采用“主会议+技术研讨会+展览展示+同期活动”的方式,举办了超过25场同期活动。峰会期间有众多企业宣布新产品或服务,吸引了超过百家企业及研究机构、开源技术社区参与。本届RISC-V中国峰会不仅是技术爱好者的盛会,也是企业展示实力和创新成果的重要舞台。

RISC-V生态视角下的商业要素必要性与重要性

本次演讲从RISC-V生态发展的关键商业化要素引入,结合目前RISC-V技术及生态概况,探讨了RISC-V CPU IP的产业价值,并展望其发展趋势与未来的协同创新模式道路,并指出RISC-V CPU的IP化已成为推动产业生态落地、商业化发展的第一步。同时借此机会向公众介绍芯来“RISC-V IP 2.0模式”,展示芯来科技的IP创新模式为芯片市场带来的独特价值。

▼左右滑动查看更多

在22-23日会议日程中,芯来科技的众多技术专家也从不同的技术层面为大家分享了芯来一年来的技术演进与研究成果。

AI关键算子RVV性能优化 芯来科技舒卓

本场演讲舒卓重点介绍了AI关键算子RVV性能优化。以关键算子的性能对于整个模型的训练及推理影响为切入点,与大家探讨如何使用RISC-V的RVV扩展来加速AI关键算子的性能。

▼左右滑动查看更多

RISC-V CPU IP赋能AI时代创芯应用 芯来科技马越

马越向大家介绍了芯来科技针对AI应用所推出的NI ( Nuclei Intelligence) 900系列。NI900系列在VLEN=512/1024位的RVV矢量计算、NPU加速器以及标量/矢量用户自定义接口等做了硬件层面的改进,并在DSP/NN软件同样做了深度的优化,使得各类算法的运行性能得到十倍至数十倍的有效提升。

同时,芯来科技提供了标量和矢量的自定义指令与CPU原有架构的深度结合,使得矢量、标量及其自定义模块能够共享整个访存系统,获得进一步的性能优化,帮助加速芯片设计企业更有效的完成AI SoC的设计。

构建AIoT时代RISC-V处理器的

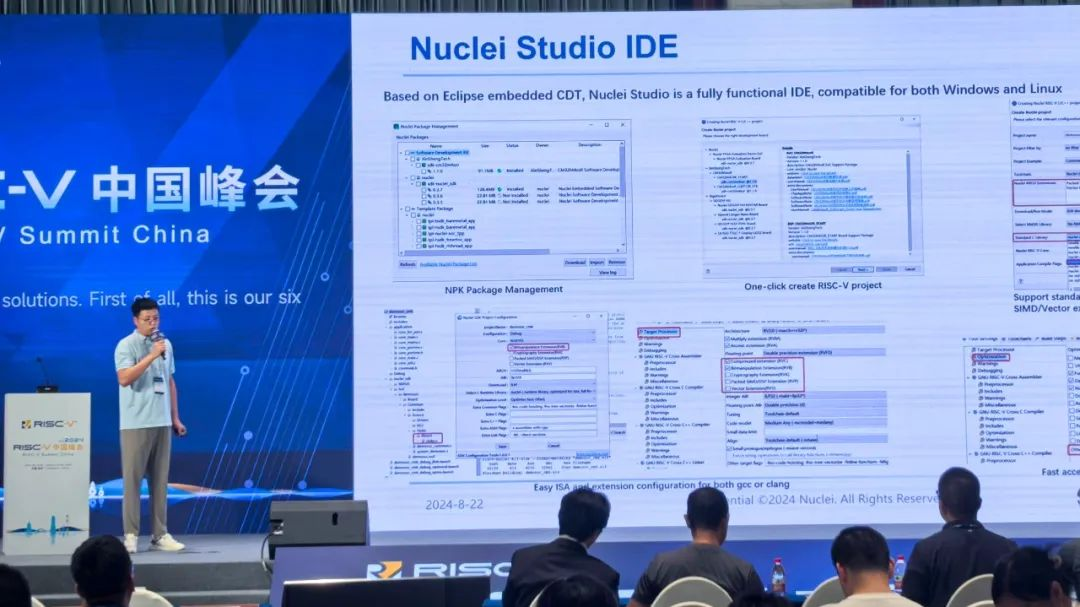

高效嵌入式集成开发环境 芯来科技方华启

在人工智能物联网(AIoT)的浪潮中,RISC-V处理器因其开放性和灵活性,成为不少嵌入式DSA/MCU芯片的选择。本次方华启的演讲深入探讨如何为RISC-V处理器构建一个高效、易用的嵌入式开发环境,以适应AIoT时代对快速开发和便捷调试,快速发布的需求。

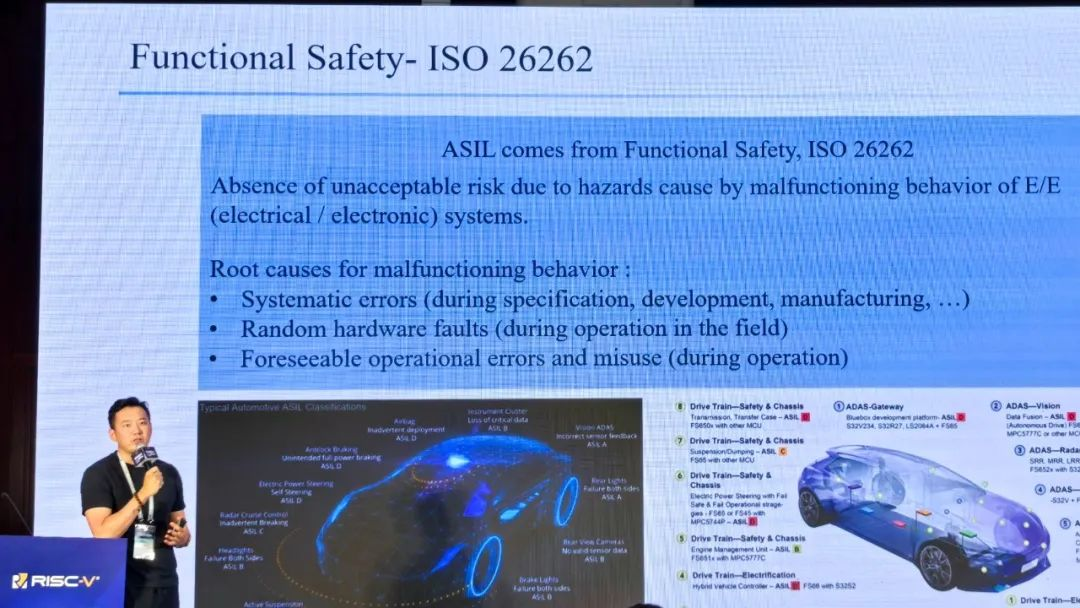

使用RISC-V CPU ASIL B/D

开发集成中的挑战与方法 芯来科技范添彬

在演讲过程中,范添彬主要分享了如何使用RISC-V开源指令集满足车规等级ASIL-D&ASIL-B解决方案,不同安全等级解决方案的客户应用情况,落地使用RISC-V国产车规芯片客户所遇到的挑战与思路。

安全加解密算子RVK性能优化

芯来科技舒卓

RISC-V架构下OP-TEE安全系统实践

芯来科技桂兵

随着RISC-V架构的广泛应用,信息安全正在成为比较突出的问题,RISC-V官方还没有正式的TEE硬件安全方案,桂兵为大家展示了芯来基于开源操作系统OP-TEE在Nuclei平台上所做的一系列安全系统尝试及研究。

基于RISC-V的HSM方案设计与实现

芯来科技王松

在本场演讲中王松重点介绍了芯来科技基于RISC-V Core的Hardware Security Module系统软硬件总体方案设计,为大家逐一解释相关流程,并呈现了demo方案的实现。

感谢各位前来芯来展位与我们交流探讨,芯来科技今后将继续携手产业链上下伙伴,以创新促发展,赋能产业生态,助力集成电路设计产业蓬勃发展!

▼往期精彩回顾▼