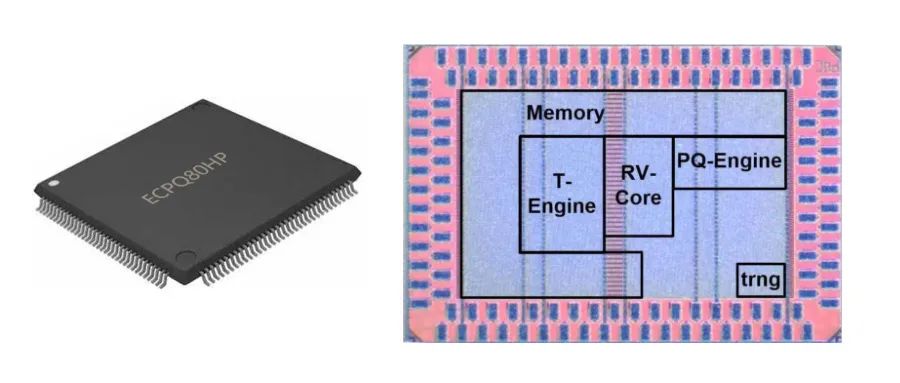

支持SIMD的混合计算兼容型

RISC-V后量子密码SoC芯片

该PQC芯片以后量子密码IP核为基础,充分利用RISC-V开源扩展指令集的优势, 建立PQC算法定制指令集,并基于可重构技术,通过定制指令对可配置硬件算子的灵活调用实现了多样化加密算法及参数的高效兼容。

该芯片具有高性能、高灵活性、高兼容性等优势,可用于多种应用领域产品的量子安全升级,芯片基本属性如下:

内置TRNG真随机数发生器

支持自定义Fast-IO高速并行传输接口(FIO)

支持2组UART接口,支持4线JTAG Debug接口

支持1组标准SPI接口,以及QSPI-FLASH接口

支持12位GPIO扩展接口

支持CRYSTALS-Kyber 512/768/1024密钥对生成算法、密钥封装算法、密钥解封装算法,峰值密钥封装/解封装性能达20万次/秒

支持CRYSTALS-Dilithium 2/3/5密钥对生成算法、数字签名算法、数字验签算法,峰值签名/验签性能达6万次/秒

支持SPHINCS+ 128/192/256 密钥对生成算法、数字签名算法、数字验签算法,峰值签名/验签性能达2千次/秒

芯片典型工作功耗29.7mW ~ 60.3mW@100MHz

支持SM2、SM3、SM4国密算法

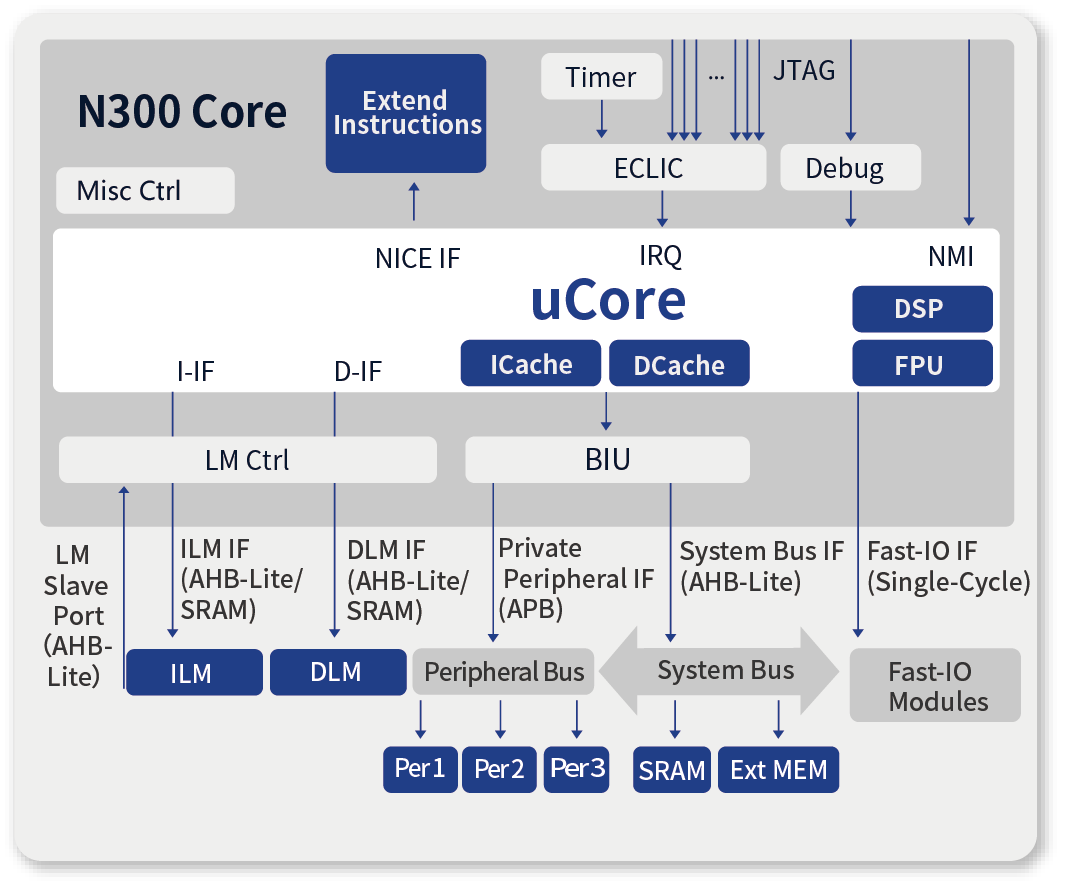

芯来N300系列处理器内核

N300可根据客户需求进行灵活配置

支持RISC-V RV32IMACFDBPKC/Zcxlcz指令集架构

支持快速中断咬尾、 中断向量化、基于优先级的中断嵌套,提供业内先进和低延时的中断特性,满足实时性的需求

可配置双发射特性

支持用户扩展自己的指令

可配置指令和数据片上SRAM(ILM/DLM)w ECC

可配置指令缓存(ICache)w ECC和数据缓存(DCache)w ECC

支持单双精度浮点和SIMD DSP扩展

支持TEE可信执行环境,满足系统安全需求

支持标准JTAG和cJTAG调试接口,以及Linux/Windows调试工具

支持RISC-V标准的编译工具链,以及Linux/Windows的图形化集成开发环境(IDE)

未来,双方将持续深化战略合作,围绕集成PQC的RISC-V IP核等关键技术展开联合攻关,共同打造覆盖多场景应用的系列化安全芯片解决方案。