RISC-V从诞生到现在已有10年时间,而就在今年的2月18日,RISC-V基金会董事长Krste Asanovic却发表博客,声称“RISC-V处理器开源”是不存在的,引发了一场关于RISC-V开源内涵的讨论。

关于这个问题我们采访到晶心科技的总经理林志明先生,他告诉与非网,“大众对于RISC-V以及「开源」或许有些误解,其实RISC-V开源的是「处理器架构」,而非提供「开源处理器」,这二者之间有技术与战略意义上的差别。所谓处理器架构指的是「指令集架构ISA (Instruction Architecture)」,而指令集架构和处理器两者间所需的开发资源及技术差距甚远。

因此,RISC-V基金会董事长Krste发表该篇博客的寓意应是为了正本清源,希望导正大众的普遍认知,将观念回归到RISC-V所开源的部分在于处理器架构,而非RISC-V处理器。”

图源 | GlobalSpec

不完全是,RISC-V处理器架构是开源的、免费的,但RISC-V处理器分为开源和商业化两种,开源RISC-V处理器不收费,而那些提供商业IP的公司通常需要大量投资,以确保那些IP在所有可量化的方面都能得到良好的支持、拥有完整的功能并具有强大的竞争力,因此是收费的。目前真正的开源RISC-V处理器并非主流且非常稀少,事实上商业化的RISC-V处理器才是主流。

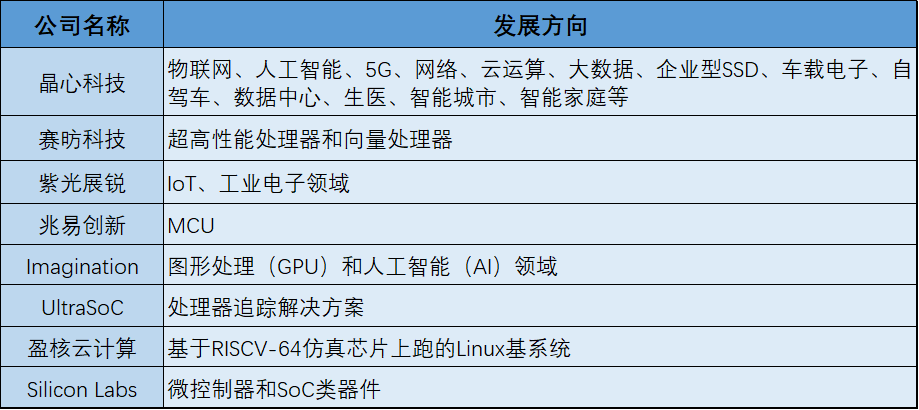

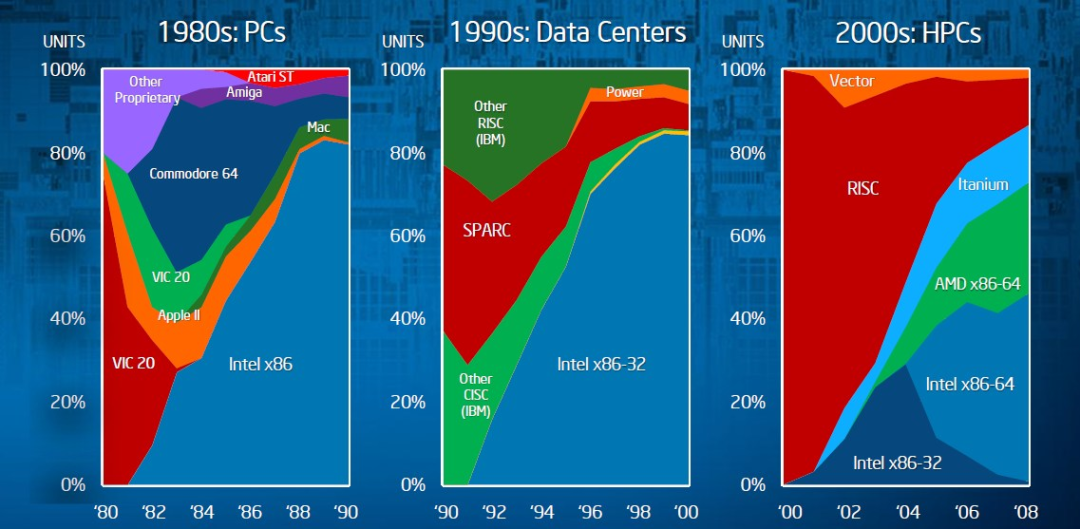

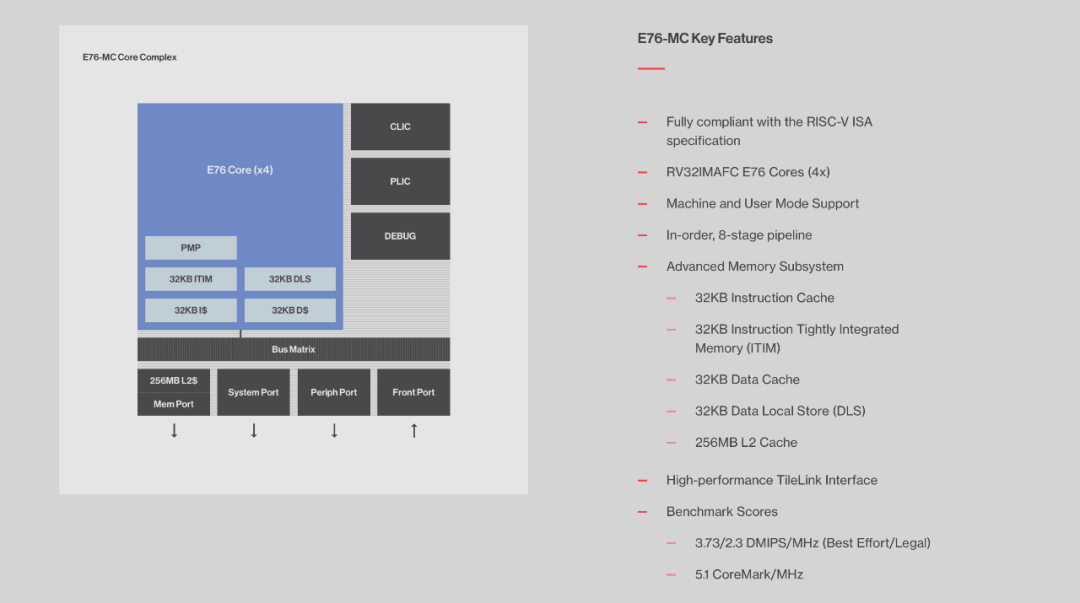

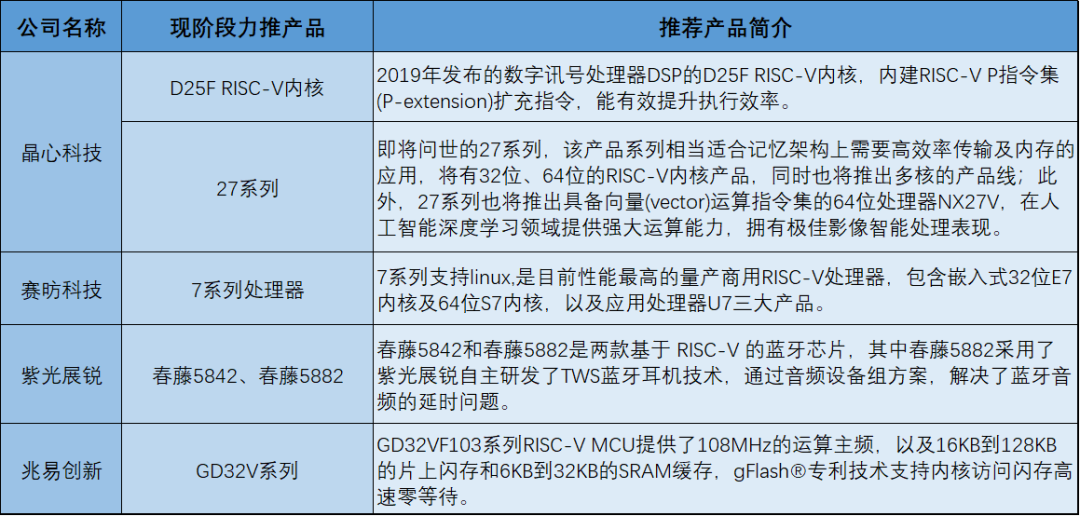

RISC-V开源指令集架构的经典案例分为两类:一类为开源处理器,由OpenHW Group、LowRISC等开源组织提供,如Rocket-chip、Pulpino;另一类为基于开源指令集的商业处理器,由非开源组织、公司或个人提供,如Si-Five系、Andes系、阿里系、晶心系、芯来系等。之所以将上述处理器称之为经典案例是基于两个原因,前一类由于出现的时间较早,对其他RISC-V处理器设计有启发和领导作用;而后一类,像SiFive系的 E3和U5是基于开源Rocket-chip所派生出的最早的RISC-V商用处理器,目前已经有大规模商业化量产记录,处理器的经典性和品质已经有所验证。就应用领域来说,分开源和商业化两部分。开源处理器中Rocket-chip应用较宽泛,可覆盖MCU、IoT及基于Linux的入门级应用;Picorv32和Pulpino比较适用于IoT应用;蜂鸟面积非常小,主要用于入门级MCU的应用。而商业化处理器的应用则根据非开源组织、公司或个人的定位所决定。图 | RISC-V国内外主流厂商与发展定位

在商业模式中,RISC-V处理器IP供货商向授权的客户提供内核设计,该设计可以是软核(soft core)或硬核(hard core)。一般软核是以RTL来作为交货依据,硬核大多是以netlist或GDSII为交货依据,目前市场主流仍以软核为主。就商业RISC-V处理器发展现状而言,国外的SiFive已具有提供64位处理器,异构多核、多cluster一致性、浮点运算/向量计算等技术能力,台湾的晶心科技也早在2018年就推出了支持64位RISC-V的主流CPU IP AndeStar V5。目前,大陆多半是RISC-V32的芯片,设计相对简单,成熟比较快,像兆易创新的GD32VF103系列、紫光展锐的春藤5842、春藤5882等。而RISC-V64处理器则主要有阿里系的平头哥半导体、芯来科技(与晶心科技合作)在研发。与非网在采访中特地了解了各个厂家的主力产品,由厂家力荐的型号与简介如下,供大家了解。

图 | RISC-V厂商力荐产品

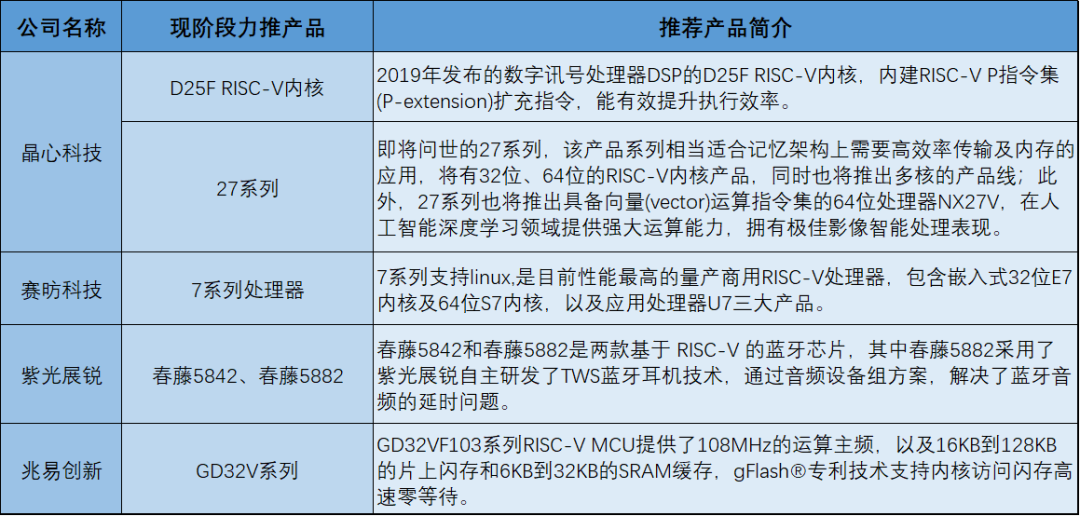

RISC-V被认为是继X86和ARM之后第三个主流架构,也被当作是“中国芯”崛起的历史机遇。RISC—V开源的优势是可以允许各家在设计芯片时,按照自己的特殊需要添加定制化的指令,满足特定应用的特殊需求,或在投票成为标准之前,将先进的创新成果先行在自己的产品中实现。然而,当这种自行添加的定制化指令逐渐增多,又不能被吸收进标准规范中时,就会产生碎片化的问题,增加成本不说,还会阻碍或延缓生态系统的完善。那么大家担心的IP碎片化,真的会成为RISC-V的送命题吗?Silicon Labs的首席技术官Alessandro Piovaccari持赞成观点,他表示,“IP重组确实是一个重要的问题,这就是为什么必须非常谨慎地使用定制化的原因。永远不要为了一点点小利益就去使用定制化。我们的理念是要对比一个有定制单元(比如无线调制解调器或者推理引擎)的混合处理器和一个不宜变更的100%全定制的完整的处理器。很多时候,一个混合处理器,尽管有IP重组的问题,但是依旧比实现完整的处理器或者实现标准处理器要容易。此外,定制版本的处理器单元应该在产品系列中重复利用,而不是逐个产品进行更改,从而可以在长期的软件维护中保持效率。”

赛昉科技的CEO 徐滔则持中立态度,他表示,“RISC-V基本的指令集是标准的,不会存在碎片化。碎片化是特定用户为满足特定产品的需求而引入的定制化指令。既然是特定产品,那么碎片化就不是问题。况且RISC-V基金会就是旨在维护指令架构的完整性和非碎片化,并且会制订若干个标准规范,在遵守这些标准规范下的定制化是被允许的,如果有公司违反了标准规范,会使他们的产品走向碎片化,从而出现各类不兼容的问题,造成与RISC-V主流生态不兼容,最终只会被孤立。事实上RISC-V的可定制化特性带来的是多样化而非碎片化,RISC-V就像一棵树的主干,而定制化则是这颗树的分枝,只要是基于主干的生长都是良性的,越来越多的分枝会让整棵大树枝繁叶茂。”

而晶心科技的总经理林志明则告诉与非网,“由RISC-V基金会所制定的RISC-V指令集模块 (ISA module) 层次是无法任意更动的,必须透过RISC-V基金会工作小组的审核才可更改,因此在这层次上的模块化架构无法由工程师自行订制,也无法更改,如此一来便不存在所谓IP碎片化的问题。”“在RISC-V引发关注前,新兴应用(例如物联网)经过数年发展渐渐成熟后,大家才发现原来物联网的应用如此零碎化,也就是说,物联网领域的需求虽庞大,但各式各样的应用中,其实每个项目的数量并不多。由于应用本身即为零碎化,因此IP碎片化的说法其实是个伪命题。”Arm架构日前对初创企业开放 图源 | 官网

要讲RISC-V和ARM的竞争,就先要从这两者的商业模式讲起,目前RISC-V的主流商业模式与ARM有些类似,但并不完全相同,RISC-V的商业模式部分为IP提供商,部分则为芯片提供商,因此,精确的说法是RISC-V与一般商业IP授权的商业模式类似。RISC-V生态正逐渐成熟,大多采用混合研发模式,ARM也将受益就目前发展状况而言,Silicon Labs的首席技术官Alessandro Piovaccari表示,“Arm的软件和工具生态系统的质量和广泛性是无与伦比的,RISC-V生态系统要达到同样的成熟度还需要一段时间,这种成熟度对于处理器的通用用途非常重要。”他还补充道,“定制化是开源RISC-V内核的主要优势,拥有开源硬件是定制化成功的关键,可以针对应用进行定制,以满足严格的功耗和实时要求,要付出的主要代价是软件需要与硬件一起进行验证,但是,这对于处理器的特定用途而言不是问题。相反,对于通用处理器而言,这是一个问题,因为它们破坏了标准和生态系统,而标准和生态系统是通用软件的基础。因此,这两类应用场景是完全不同的。”“此外,RISC-V的发展产生的多种使用范围很广的内核正在推动SoC开发者在其产品中使用越来越多的内核。传统上只有一个内核的器件现在可能会有五个或者更多内核。即使是固定功能的产品,现在也会有一个RISC-V微内核。这种“处处安放微内核”的理念正在扩大多内核处理器的市场。这也将使Arm受益,虽然Arm的市场份额可能会减少,但整个市场体量将大幅增长,因此Arm也会实现更高的增长。”而Imagination Technologies CPU硬件工程副总裁Steven Yeung则告诉与非网,“目前很多公司采用的是混合研发模式,采用这种研发模式的原因有两点:一是RISC-V技术或现有的RISC-V内核还没有形成一个公平竞争的环境,二是从一种架构迁移到另一种架构需要时间,对于第二点原因,情况将会改变。现在,有许多低端的RISC-V产品,但是随着时间的推移,人们将在中高端市场中看到有竞争力的内核,RISC-V将获得更大的市场份额。”

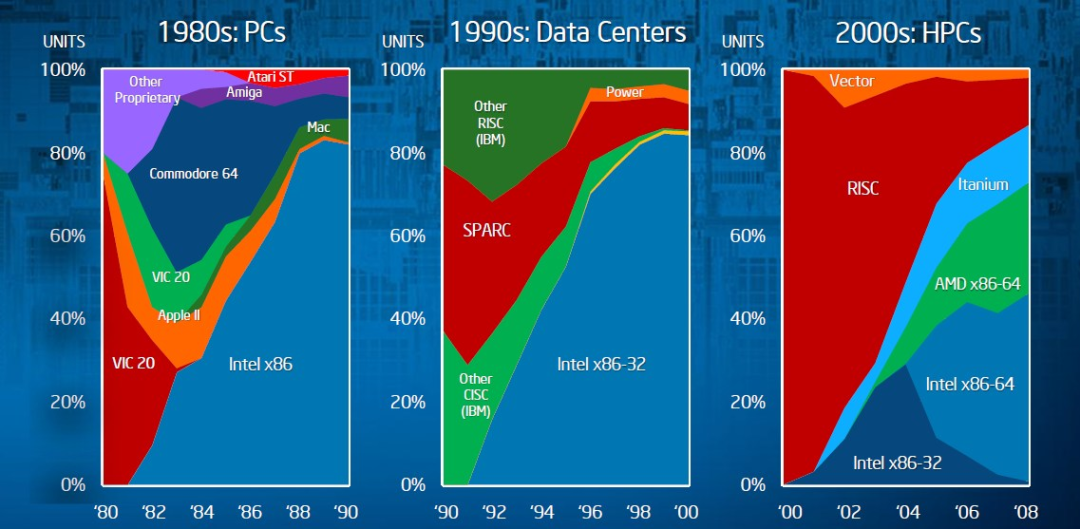

图源 | Extreme Tech

“一种架构的兴起并不代表其他架构的消亡,RISC-V与X86和ARM架构未来将呈现三足鼎立之势力。多年来ARM在Android端一直占据主流,X86在服务器端后也始终处于垄断地位,相比两大传统架构,新生代架构RISC-V显然更具活力,目前已实现了在AI及IoT等新兴领域率先登陆,并且正向更多的领域延伸。未来这三大架构都会各自占据固有的领地,并在交集市场产生竞争,市场足够庞大,必要的良性竞争有助于处理器技术及商业模式的不断创新和优化,对于整个市场来说是有益的。”赛昉科技CEO 徐滔如是说。与非网评论:假设市场容量不变,RISC-V将会抢占部分ARM市场,但现实是市场容量会随着物联网、人工智能等领域的爆发而不断攀升,因此未来RISC-V抢占的只是ARM或X86的份额占比,在总量上,三者都会呈上升态势。

可预见的是,未来2-3年RISC-V高性能应用在服务器、移动端及车载电子等领域将会有更多实现,在IOT/MCU等领域RISC-V会更加有活力,而基于应用软件的技术及生态也将持续增进,并且在特定领域,如DSP/AI/图像/网络领域也会有所斩获。同时,基于应用的软件工作将大量展开,如 Hypervisor、矢量、安全、功耗管理、服务器等方面。同时,基于RISC-V指令集架构的芯片将以几何倍增的速度发展。三星RISC-V芯片构造 图源 | wccftech

以高通、三星、西数为首的半导体厂商均已不同程度的投入到基于RISC-V的产品线,以芯片研发的一般周期来看,未来2-3年将会陆续有芯片问世,尤其在AIoT、IIoT、5G等领域将会有更多基于RISC-V的产品问世。而龙头厂商的稳定出货必将导致大量观望者果断跟进采用RISC-V技术,因此RISC-V的使用者数量还将暴增。此外,基金会和联盟也将通过搭建产业交流平台,推动RISC-V技术的广泛应用、建立长效合作机制,并促进RISC-V教学科研与产业人才培养、加速产业发展。与非网评论:RISC-V市场看好,生态的完善是RISC-V取得商业成功的关键,而标准化和多元化是RISC-V快速发展的基石。

RISC-V已经有10年历史,却在过去一年内突然爆发,已经初步经历了从学术到实际商业应用的过程。RISC-V凭着指令集开源等特性有机会占据可观的市场份额。物联网市场有碎片化、多样化的特点,拥有众多细分领域,RISC-V可以针对不同应用灵活修改指令集和芯片架构设计的优势就体现出来了。此外,物联网市场对于成本较敏感,RISC-V开源免授权费的特点也将吸引更多的厂商。借用UltraSoC亚洲销售副总裁 Lisa Yang的原话,“在很多时候,尽管工作是不断的,但进展似乎是在一系列的“跳跃”中发生,而不是一条稳定的曲线。”话外之音,大量投入之后,总会在某个特定的节点上看到成功的曙光。大胆地猜想,假设今年如果没有疫情,RISC-V 将会是一个投资热点吧,一定会有许多生态环节在今年得到建立。中关村科学城开源芯片源码创新中心(Beijing Open Source Silicon Innovation Center, BOSSIC)由海淀区政府、北京市科委、微芯研究院等单位共同发起,旨在聚焦芯片研发源头创新,布局全球标准,打造高质量国际开源平台,助力芯片人才培养,营造海淀区“硬核”创新氛围,推动国家芯片产业创新发展。

长按识别二维码关注北京开源芯片源码创新中心

联系我们:comms@baec.org.cn