欧盟RISC-V芯片的更多细节曝光

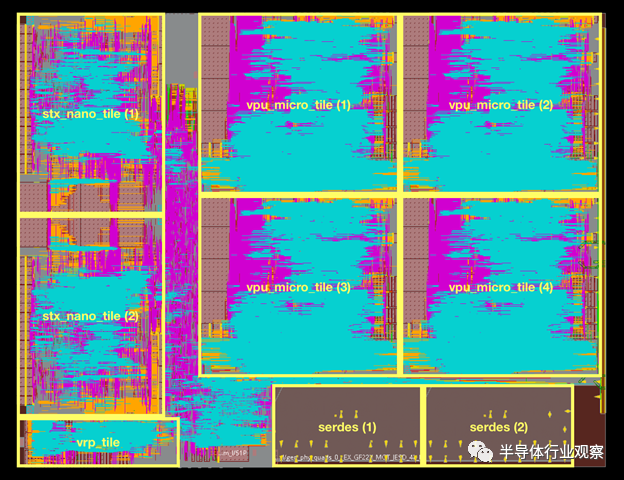

近日,一个由来自 10 个欧洲国家的 28 个合作伙伴组成的,旨在帮助欧盟在 HPC 芯片技术和 HPC 基础设施方面实现独立的项目EPI(The European Processor Initiative)宣布 ,已成功发布其基于RISC-V架构的EPAC1.0 测试芯片。EPI 活动的一个关键部分是开发和演示基于 RISC-V 指令集架构的完全由欧洲开发的处理器 IP,提供名为 EPAC(欧洲处理器加速器)的高能效和高吞吐量加速器内核。使用 RISC-V 指令集架构将允许在硬件架构和软件级别利用开源资源,并确保独立于非欧洲专利计算技术。EPAC 结合了多种专门用于不同应用领域的加速器技术。测试芯片如上图所示,包含四个VPU(vector processing micro-tiles),由SemiDynamics设计的Avispado RISC-V内核和巴塞罗那超级计算中心和萨格勒布大学设计的矢量处理单元组成。每个 tile 还包含一个 Home Node 和 L2 缓存,分别由 Chalmers 和 FORTH 设计,提供了内存子系统的连贯视图。模板和张量加速器 (STX) 由 Fraunhofer IIS、ITWM 和 ETH Zürich 设计,VRP(variable precision processor )由 CEA LIST 设计。这些专用加速器与 EXTOLL 的超高速片上网络和 SERDES 技术相连接。EPAC 设计由 Fraunhofer IIS 完成,并在GLOBALFOUNDRIES 22FDX 低功耗产线上完成芯片集成,并将在 FORTH、E4 和萨格勒布大学设计的基于 FPGA 的电路板中进行集成和评估。EPAC的成功制造将展示基于加速器的绿色HPC计算的下一步。根据他们的展望,下一代 EPAC 加速器和接口将得到改进和完善,以在 12 纳米及以下技术中实现更高的性能和更低的功率水平,并计划引入小芯片方法。来自 Fraunhofer IIS 的 Norbert Schuhmann 说:“这种设计和架构的关键挑战不仅在于在超过 1 GHz 的加速器中实现最高的吞吐量和低功耗水平,而且还要像协奏曲一样与内存访问和芯片内部和外围设备的数据传输速率高于 200 Gbit/s。”

根据EPI的最初规划,这些处理器的第一代芯片预计在2020年推出,以便及时地为欧盟将在2020-2021年间部署的E级先导系统提供支撑,而第二代芯片将于2023-2024年助力欧盟的第一套E级系统。这项系统工程由EuroHPC(欧洲超算联盟)主导,该组织成立的初衷就是使欧洲在高性能计算技术方面与美国、中国和日本并驾齐驱。这项任务的部分工作涉及开发自研组件,以增强欧盟成员国对超级计算机的自主可控能力。但从最新的报道可以看到,EPI最新的的目标是到2022年将把ARM和RISC-V的组合芯片用于高性能计算(HPC),这比原计划晚一年。项目项目合作伙伴已经完成了其RISC-V加速器体系结构的第一个版本,名为EPAC,并预计在明年的三年项目结束之前测试芯片。代号为Titan的EPAC测试芯片芯片将与PCIe EPAC测试平台相辅相成,可以测试和增强体系结构,以备将来修订和构建原型系统。该项目旨在到2022年,在台积电的6nm工艺上生产使用ARM Zues和RISC-V内核生产代号为Rhea的多核设备。按原定时间表计划,这将在2021年完成。代号为Cronos的第二代设备将结合包括EPAC加速器与ARM Neoverse V1高性能数据中心核心。这将是2023年建造欧洲百亿亿次超级计算机的主要引擎。RISC-V的先驱SiPearl一直是这个项目的关键人物,SiPearl与Arm签署了许可协议并在德国开设了一家分支机构。竞争对手SiFive还与巴塞罗那超级计算机中心以及EPI合作伙伴合作,为百亿亿超级计算机使用RSIC-V技术。“SiFive在百亿亿次计算非常感兴趣,我们与BCS Barcelon合作,使用的是一个完整的系统模型的模拟框架,并增加了RISC-V标准的向量处理器,使exascle处理更加强大,”SiFive性能架构的高级总监Nasr Ullah说。EPI项目已经具有支持RISC-V向量内在函数和C / C ++代码自动并行化的编译器,并且正在仿真中评估生成的代码平台可为应用程序,编译器和体系结构的整体协同设计提供详细的见解。其他软件开发工具(SDV)正在为异构ARM + RISC-V体系结构调整操作系统。该芯片不仅涉及百亿亿次超级计算机。该项目还正在为汽车工业开发概念验证,以展示欧洲处理器倡议IP如何实现未来的ADAS功能,从而为通过RISC-V平台,Kalray的MPPA和EPAC加速EPAC加速器铺平道路。Menta eFPGA IP作为加速器。

*免责声明:以上内容仅供交和流学习之用。如有任何疑问或异议,请留言与我们联系。