1

https://riscv.org/whats-new/2022/02/intel-corporation-makes-deep-investment-in-risc-v-community-to-accelerate-innovation-in-open-computing/

「见证历史:Intel加入RISC-V国际基金会」

https://mp.weixin.qq.com/s/XXmVuCVXFBuFF9EAs3-91w

——CNRV

2

https://riscv.org/risc-v-mentorship-program/

「RISC-V国际实习项目报名2月13日截止,同学们请抓紧时间准备!」

https://mp.weixin.qq.com/s/pCIkWgdU3L1ga2SKCYjawg

——CNRV

3

「第三大CPU架构RISC-V崛起了:单厂商年出货超30亿」

https://g.pconline.com.cn/x/1483/14831930.html

——知科技

4

「北京君正:目前RISC-V的CPU核尚在设计阶段 尚未确定后续具体芯片的制程」

https://finance.eastmoney.com/a/202202082269748658.html

——每日经济新闻

5

RISC-V早已获得超乎寻常的关注,被寄予引领物联网时代新风潮的厚望。中国工程院院士倪光南曾多次提出,未来世界主流CPU架构格局中,三分天下有其一。

除了物联网,RISC-V“上车”似乎风向愈明。

「RISC-V“上车记”:仅锦上添花,难雪中送炭?」

https://baijiahao.baidu.com/s?id=1724065008591193805&wfr=spider&for=pc

——集微网

6

RISC-V体系结构的一个主要优势是它的开放性,因此任何具有适当技能的组织都可以开发自己的处理器IP。印度政府利用微处理器开发计划(MDP)的机会开发VEGA RISC-V处理器IP。

得益于电子和信息技术部(MeitY)的资助,先进计算发展中心(C-DAC)成功设计了五种RISC-V处理器,从单核32位RISC-V MCU级处理器到支持Linux的四核64位乱序处理器。

「印度使用VEGA处理器实现RISC-V」

https://www.cnx-software.com/2022/02/04/india-goes-risc-v-with-vega-processors/

——CNX

7

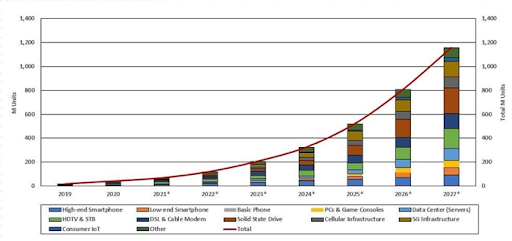

「Semico Research的新报告预测:到2027年基于RISC-V的人工智能SoC将达到250亿颗」

https://riscv.org/blog/2022/02/semico-researchs-new-report-predicts-there-will-be-25-billion-risc-v-based-ai-socs-by-2027/

(图片来源:RISC-V国际基金会)

——RISC-V国际基金会

8

可编程门阵列(FPGA)是一种集成电路(IC),可用于实现自定义数字电路。您可以使用FPGA为数字信号处理(DSP)、机器学习和加密货币挖掘等创建优化的数字逻辑。由于FPGA的灵活性,通常可以使用其数字逻辑实现整个处理器。您可以在消费电子产品、卫星和用于执行专门计算的服务器中找到FPGA。在本系列中,我们将了解FPGA如何工作,并演示如何使用Verilog硬件描述语言(HDL)创建自定义数字逻辑。

「FPGA简介第12部分——RISC-V定制外设」

https://riscv.org/news/2022/01/introduction-to-fpga-part-12-risc-v-custom-peripheral-shawn-hymel-digi-key-electronics/

——RISC-V国际基金会

9

根据协议条款,SmartDV将在北美、中国、印度和中国台湾地区销售基于32位RISC-V ISA的高可靠性通用CPU NS31A。NS31A设计用于控制各种嵌入式系统,支持汽车应用所需的ISO 26262 ASIL D级功能安全机制和AUTOSAR平台所需的特权模式。

「SmartDV™和NSITEXE签署协议,在北美、中国、印度和中国台湾地区部署NSITEXE的RISC-V 32位CPU核心」

https://riscv.org/news/2022/01/smartdv-and-nsitexe-sign-agreement-to-deploy-nsitexes-risc-v-32bit-cpu-core-throughout-north-america-china-india-taiwan-smartdv/

——RISC-V国际基金会

10

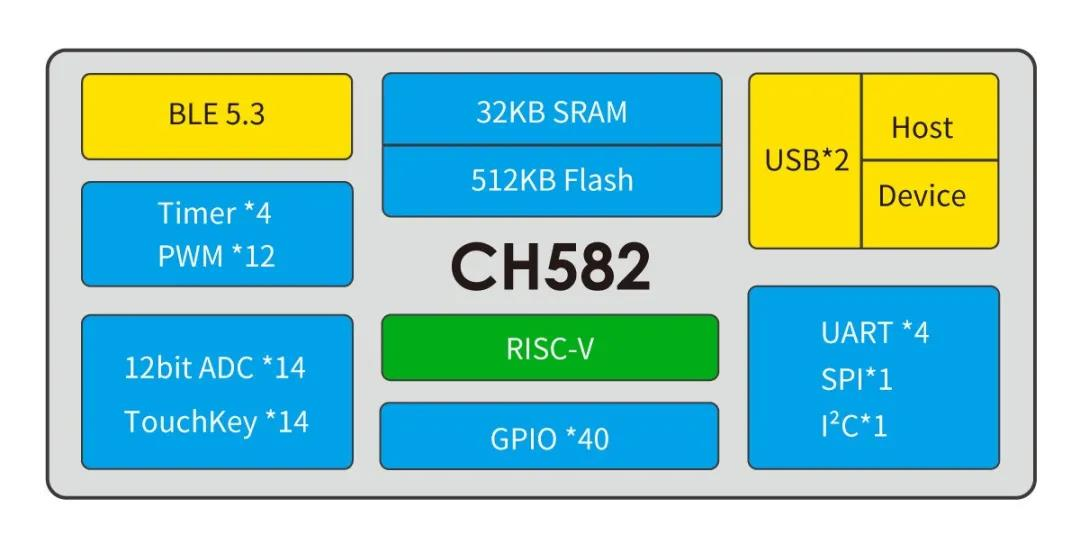

「支持休眠唤醒的低功耗触摸方案」

https://mp.weixin.qq.com/s/UFIatMU7DqyrxBH5At2Yjw

(图片来源:沁恒微电子)

——沁恒微电子

11

「你确信你的RISC-V RTL里没有任何Bug么?」

https://semiengineering.com/do-you-know-for-sure-your-risc-v-rtl-doesnt-contain-any-surprises/

——Semiconductor Engineering

12

「RISC-V应用于网关」

https://riscv.org/news/2022/02/gateway-implementations-with-risc-v-alex-pluemer-mouser-electronics/

——RISC-V国际基金

13

传统上,计算机体系结构是在大学环境中作为讲座和教科书课程学习的,带有实验室组件。利用TL Verilog和Makerchip,下面的课程从一开始就是实验课程,在实践中学习理论。

虽然这些课程涵盖了不同深度的内容,但它们都从逻辑门开始,并指导您构建一个简单的基于RISC-V的CPU。

「RISC-V CPU设计课程」

https://riscv.org/news/2022/02/risc-v-cpu-design-courses-redwood-eda-llc/

——RISC-V国际基金会

1

——快科技

2

https://36kr.com/p/1606354790058757

——36Kr

3

https://baijiahao.baidu.com/s?id=1724195020785112937&wfr=spider&for=pc

——三易在线

https://zhuanlan.zhihu.com/p/463582269

OSTD Weekly (第136期·2022-02-09):

更多实验例程

www.rvmcu.com