近日,本土专业RISC-V处理器IP及解决方案公司芯来科技与专业虚拟仿真工具及解决方案公司杭州芯芒科技共同宣布达成战略合作。

芯芒科技的Mosim系列仿真验证工具将全面支持芯来全系列RISC-V处理器IP,帮助下游芯片公司尤其是大型SoC设计团队快速创建整芯片&系统虚拟原型,并提供一系列高效的软硬件开发工具,助力客户产品加速上市,共同促进RISC-V产业的发展和变革。

协同创新

众所周知,传统大型SoC的串行开发流程复杂而冗长,特别是早期系统架构探索往往很难准确评估架构性能功耗、效率低下且容易出现错误;同时功能验证、产品软件开发和性能优化都依赖于FPGA或者Emulator等硬件工具,在芯片整体前端开发完成之后才能陆续展开,迭代周期长,风险极大。

随着RISC-V生态的逐渐完善,越来越多的芯片及系统厂商已经开始布局基于高性能RISC-V 处理器的大型SoC。然而大型SoC的模型、仿真和软件模拟开发都离不开EDA工具来支撑。

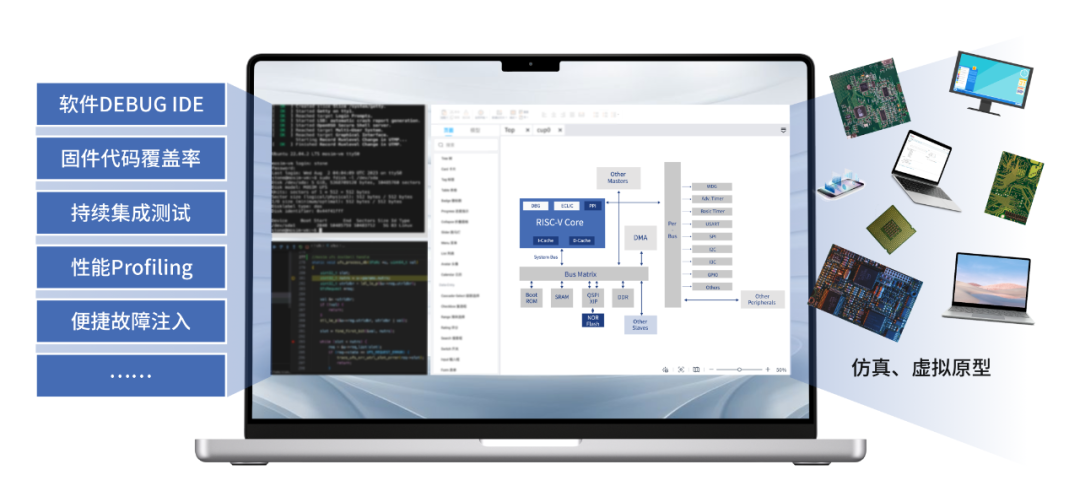

芯芒科技为本土的芯片&产品研发团队提供端到端虚拟仿真解决方案,以应对越来越复杂的芯片设计及验证挑战。基于芯芒科技自主研发的Mosim仿真平台可以快速构建从芯片核心架构、整芯片到全系统的虚拟原型,高效开展芯片架构探索、芯片&产品软件开发以及整系统性能&功耗的深度优化,实现软硬件开发并行解耦,支撑产品竞争力提升的同时,大幅缩短芯片&产品研发周期。

芯芒Mosim针对RISC-V CPU为芯片设计公司提供了丰富的功能:

快速支持RISC-V定制场景,同时支持处理器异构仿真

支持芯片早期架构探索,准确评估系统性能&功耗,高效开展IP选型、软硬件划分等工作

实现软件在RTL Ready前3~6个月提前开发,提供Debug IDE,无侵入式代码覆盖率、敏捷故障注入等高效的研发工具

支持业界SystemC TLM2.0标准,仿真性能领先行业水平

兼容Qemu、Verilator等第三方仿真工具/平台,支持与真实环境联接,为用户提供全方位的仿真解决方案

基于Mosim平台整体优化后可以极大缩短大型SoC芯片的整体研发流程和周期。Mosim支持Cycle Accurate时钟精确、Cycle Approximate时钟近似以及Programming View程序员视角等不同精度建模仿真。在架构设计初期即可实现架构模拟,快速迭代最优架构设计,降低架构决策风险;之后根据芯片设计的进度快速迭代虚拟原型,支撑软硬件验证工作可提前FPGA数个月开启;产品开发团队无需等待投片,在功能充分验证后即可启动软件的开发和优化工作。

此次战略合作发挥了双方各自的资源优势,芯来科技的高性能RISC-V处理器IP,联合芯芒科技的虚拟仿真平台及解决方案,相信未来能够共同为大型RISC-V SoC设计客户提供更敏捷高效的完整解决方案。

▼往期精彩回顾▼

芯来科技发布最新NS100内核IP,完善全系列信息安全内核布局

芯来发布NI系列内核,NI900矢量宽度可达512/1024位

芯来科技携手西门子EDA,推进RV CPU Trace完整解决方案

芯来携手战略伙伴为RISC-V CPU IP提升DFT可测试性设计

芯来科技荣获中国开放指令生态(RISC-V)联盟“IP先锋奖”

亮相国际舞台 | 芯来RISC-V CPU IP北美峰会引关注