财联社4月19日电,北京市经济和信息化局印发《北京市加快建设信息软件产业创新发展高地行动方案》。其中提到,面向具身智能、XR设备、智能计算机、车载终端、物联网设备等新终端,引导软硬件协同创新。前瞻布局具身智能,加强人工智能企业与机器人、重大装备制造企业对接。采用设备厂商出题,企业揭榜方式,组织攻关空间计算、内容渲染等关键技术。以头部PC厂商为链主,推动芯片指令集创新,推进新型芯片、主板等硬件适配调优工作,支持研发智能体操作系统、PC端智能应用等新型软件。组织车企与信息软件企业结对攻关,加强车规级芯片、车载软件、大模型技术融合创新,推动自动驾驶中间件落地,加速智能界面软件上车,研发汽车软件大模型开发工具。建立物联网设备互联互通技术标准,支持底层物联网操作系统开源,结合高端传感器、物联网芯片、新型短距离通信、高精度定位等设备开发软件中间件。提前谋划、组织攻关RISC-V芯片的操作系统内核、编译器等底层软件,实现芯片研发与软件迭代同步。

「北京:提前谋划、组织攻关RISC-V芯片的操作系统内核、编译器等底层软件,实现芯片研发与软件迭代同步」

为推动开放指令集标准与EDA产业标准进一步合作,4月19日,RISC-V工委会在上海参加由EDA²主办的第三届EDA标准全会,双方在全会上举行了战略合作签约仪式。EDA²秘书长曾璇、RISC-V工作委员会秘书长周萌分别代表各自组织签约。

「推动开放指令集标准与EDA产业标准协同,RISC-V工委会与EDA²共筑芯生态」4月25日,由北京市科学技术委员会、中关村科技园区管理委员会、河北省科学技术厅、河北雄安新区管理委员会主办的2024年中关村论坛雄安空天产业创新论坛在雄安国际酒店举办。600位国内外专家学者齐聚雄安,是中关村论坛首次在年会期间于京外举办的平行论坛。中国移动芯昇科技有限公司总经理肖青表示,雄安新区坚持城市发展自主可控,对RISC-V产业发展有独特优势。通过成立雄安新区未来芯片创新研究院,探索新模式、解决新问题,将进一步推动雄安新区成为自主创新的策源高地,助力雄安新区建设成为“RISC-V之城”,赋能雄安新区发展新质生产力。

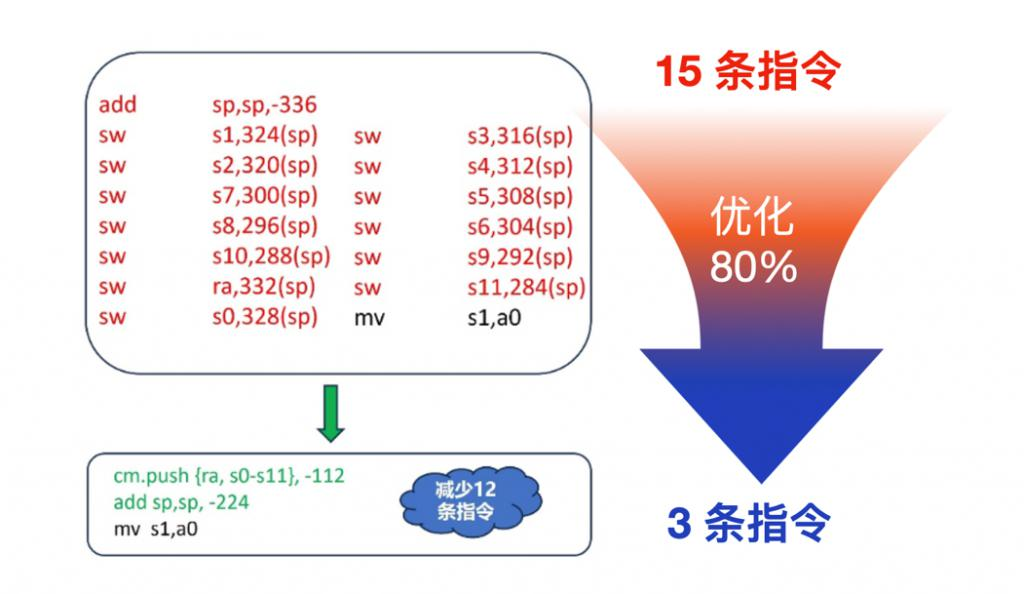

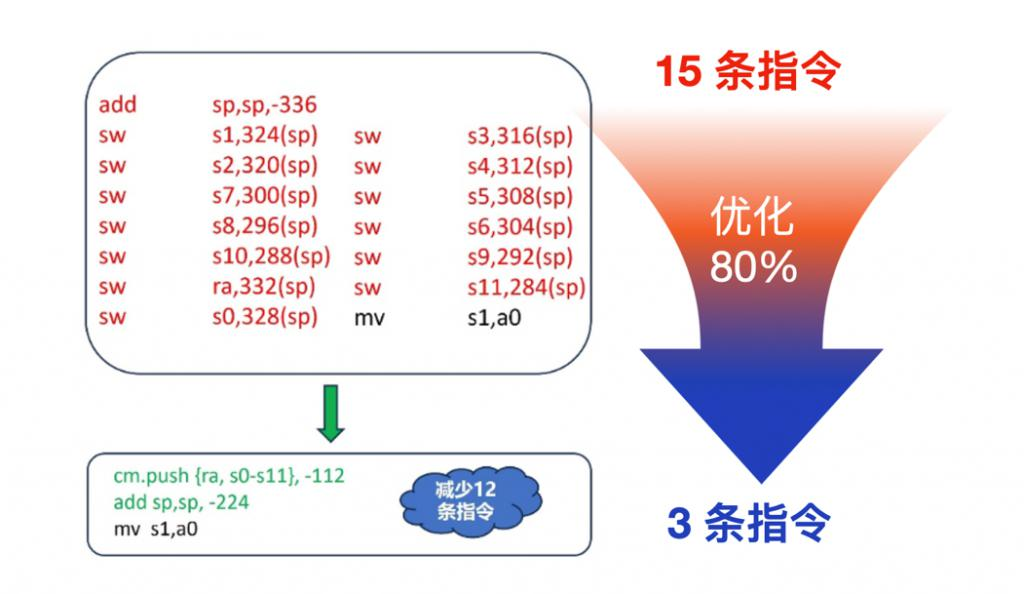

芯来科技作为国内领先的RISC-V CPU IP和解决方案供应商,其CPU IP应用领域广泛,覆盖从低功耗到高性能的各种应用需求。兆松科技近期发布的ZCC工具链已全面支持芯来科技RISC-V处理器内核,包括芯来科技自定义扩展指令集Xxldsp(n1/n2/n3) 和Xxlcz,为芯来科技及其合作伙伴提供更多的选择,以达到更高的代码密度和性能,从而满足更加广泛的市场应用需求。「软硬协同 | 芯来RISC-V IP引入兆松ZCC工具链,进一步丰富软件生态」

图片来源:芯来科技

经过2023年持续的功能开发与性能/频率/功耗优化,进迭时空的第二代RISC-V高性能核X100的研发工作全部结束,可交付量产。X100是一款面向服务器CPU芯片研发的RISC-V高性能核,采用4发射乱序架构,通用计算性能Coremark达到7.7/MHz,Spec2k6超过8.2/GHz,在12nm工艺下频率可达到2.5GHz,各项指标均超过设计预期。

「研发收关:高性能处理器核X100完整符合服务器规格要求」

图片来源:进迭时空SpacemiT

位于“印度硅谷”的初创公司CalligoTech,专注于开发针对HPC、大数据和AI/ML的产品和解决方案,推动了Posit算法在硬件和软件领域的商业化。该公司最近推出的加速器TUNGA采用了基于Unum的新一代算术技术,并且是首款应用Posit的多核RISC-V处理器。借助新思科技的数字设计系列,CalligoTech成功完成了这款处理器的流片工作,并正在致力于交付更高能效的CPU。

「150万门级+Posit+RISC-V,这款新一代大规模计算芯片流片成功」

24.03新版本发布在即,为促进开发者和社区用户之间的交流,2024年4月21日, OpenAtom openEuler (简称"openEuler") RISC-V SIG和Compiler SIG联合苦芽科技在上海联合举办了一场Meetup活动。

活动现场,来自openEuler社区、苦芽科技的30多名专家及参会者面对面交流,共同探讨openEuler的新技术特性、版本进展、RISC-V架构、编译器、虚拟机最新进展,并重点讨论「LLVM平行宇宙计划」的路线图实施情况。「活动回顾 | RISC-V SIG & Compiler SIG Meetup上海站」一位PLCT实验室不善言辞的实习生肖世杰同学,完成了ThreadX的RISC-V移植并已经开源到了GitHub。Upstream所需的代码整理工作已经在做了,相信很快就能开始进入上游。

「快讯|ThreadX RISC-V移植完成,可以跑在Milk-V Duo上了!实习生立大功」近日,Rivos传出了好消息,那就是他们拿到了2.5亿美金投资。他们也在这次融资之后,公布了公司的一些芯片规划。

「MTK和Intel联手,投资RISC-V芯片新贵!再战英伟达?」2024中关村论坛年会4月25日开幕,第三代“香山”开源高性能RISC-V处理器核作为重大科技成果之一发布。其性能水平已进入全球第一梯队,可广泛应用于服务器芯片、AI芯片、GPU、DPU等高端芯片领域,为先进计算产业提供开源共享的共性底座技术。

「第三代“香山”开源高性能RISC-V处理器核发布」4月29日,在“创芯·生生不息——进迭时空2024年度产品发布会”上,进迭时空创始人、CEO陈志坚博士发布了全球首颗8核RISC-V AI CPU——SpacemiT Key Stone™ K1(简称K1),用一项项实测数据证明:在满足AI算法模型快速迭代和部署方面,同等微架构的RISC-V芯片至少领先ARM芯片1.5代。

「领先1.5代,全球首颗8核RISC-V AI CPU发布」为解决RISC-V架构在嵌入式领域的应用瓶颈,隼瞻科技针对代码密度增强技术开展了全方位革新,从最源头最核心的处理器指令集进行了大幅优化。

首先,隼瞻处理器对RISC-V社区多年来陆续引入的B扩展、Zc扩展、Zicond等一系列标准扩展提供了有效支持。「全面革新RISC-V架构,隼瞻科技代码密度增强技术为嵌入式芯片创造更多可能」

图片来源:Zaker

4月19日消息,三星电子将扩大其在美国硅谷的研发(R&D)机构,以专门设计人工智能(AI)芯片。在以人工智能芯片为重点的半导体行业重塑中,三星计划增强其设计能力,以颠覆目前由英伟达等美国大型科技公司主导的市场。

三星旗下SAIT(前身为高级技术学院)已在硅谷建立先进处理器实验室(APL),专门从事AI芯片设计。APL正在开发下一代半导体设计,重点关注RISC-V领域。RISC-V是半导体芯片设计的基础标准,该领域主要由英国半导体设计公司ARM垄断。三星的RISC-V举措被解读为迈向技术独立的一步。4月15日,巴塞罗那超算中心和ELDORADO研究所签署了合作协议,共同推进巴西RISC-V技术发展,以突破高性能计算和人工智能的边界。

「巴西和欧洲签署HPC RISC-V技术创新项目」

据报道,Arm中国前首席执行官Allen Wu(吴雄昂)已经成立了一家新公司,将开发基于RISC-V指令集架构的芯片。中智芯片(上海)科技有限公司会在某些方面挑战Arm和Arm中国。与此同时,有传言称该公司可能成为Tenstorrent在中国的“代表”。

「前Arm中国CEO创立RISC-V处理器初创公司」SYSGO发布了其支持RISC-V的linux操作系统——ELinOS 7.2。该平台完全支持Microchip的PolarFire SoC Icicle,并修复了2038漏洞。「SYSGO发布ELinOS7.2版本,支持RISC-V嵌入式Linux」——Embedded Computing Design

连续7年营收增长的RISC-V公司,AI产品占比最高?

从芯来到“香山”,芯华章助力国产RISC-V生态做了哪些事?

OpenArkCompiler Weekly(第210期·2024-4-28)

开源开发工具周报OSDT Weekly(第251期·2024-4-24)

https://mp.weixin.qq.com/s/nk36ux4HXpQ7N3uro4zv3w