喜欢1次

队名:newbird

队号:CICC2469

https://www.rvmcu.com/community-topic-id-386.html

以上链接为如何生成.verilog,并在VIVADO中生成波形的例子。我们在实践过程中,发现了两个小问题,在上述帖子的评论区也有很多同学问过,所以分享一下。

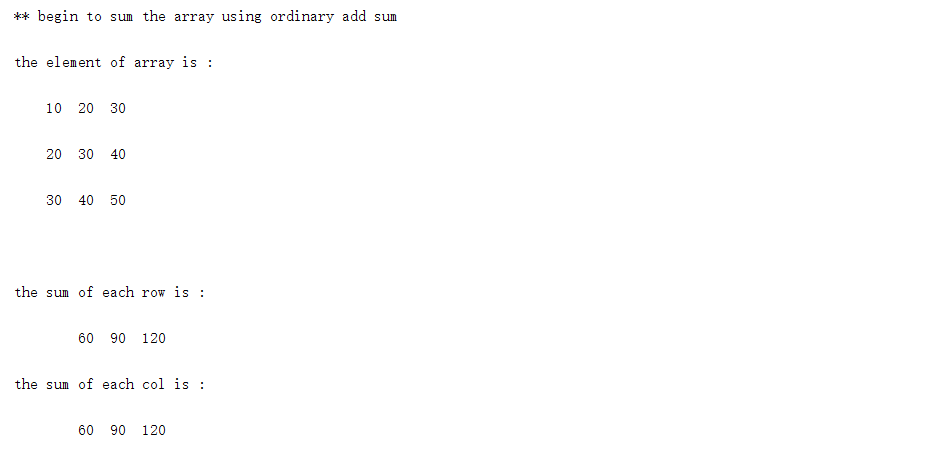

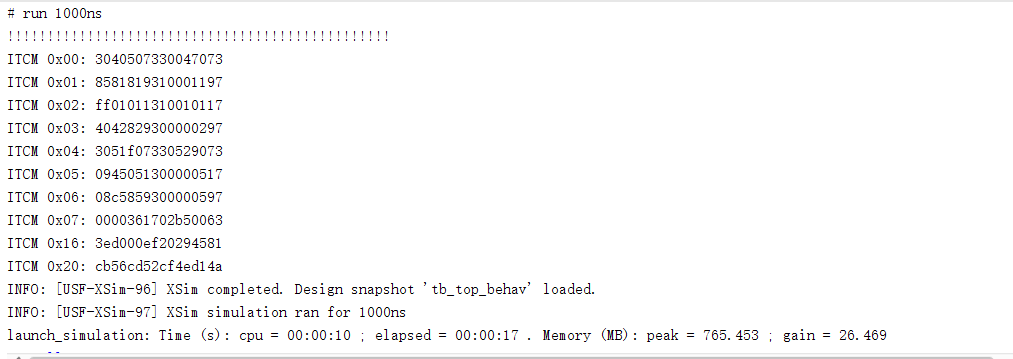

一、运行之后,发现控制台没有打印main.c函数中的内容,而是如下图所示

这是因为仿真时间1000ns太短,设置运行时间为100us,就可以看到控制台输出想要的内容了

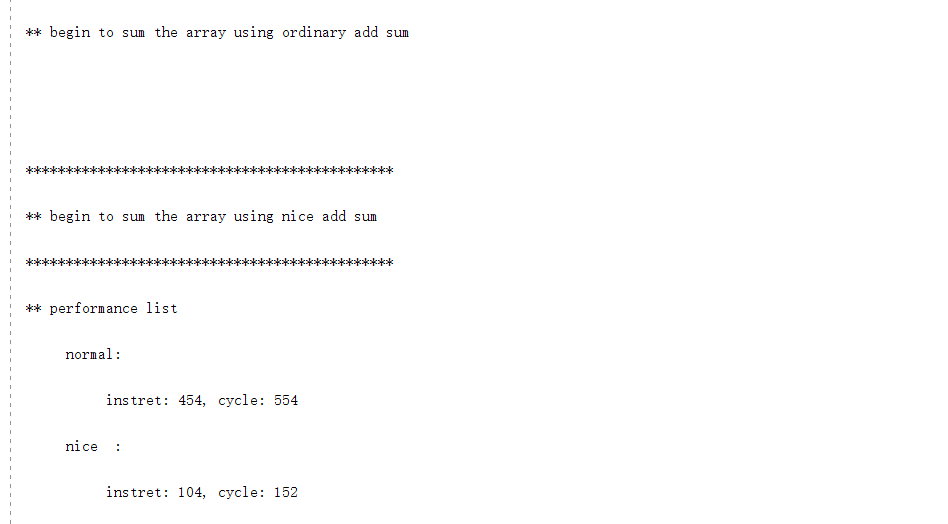

二、运行了100us,但是控制台输出如下

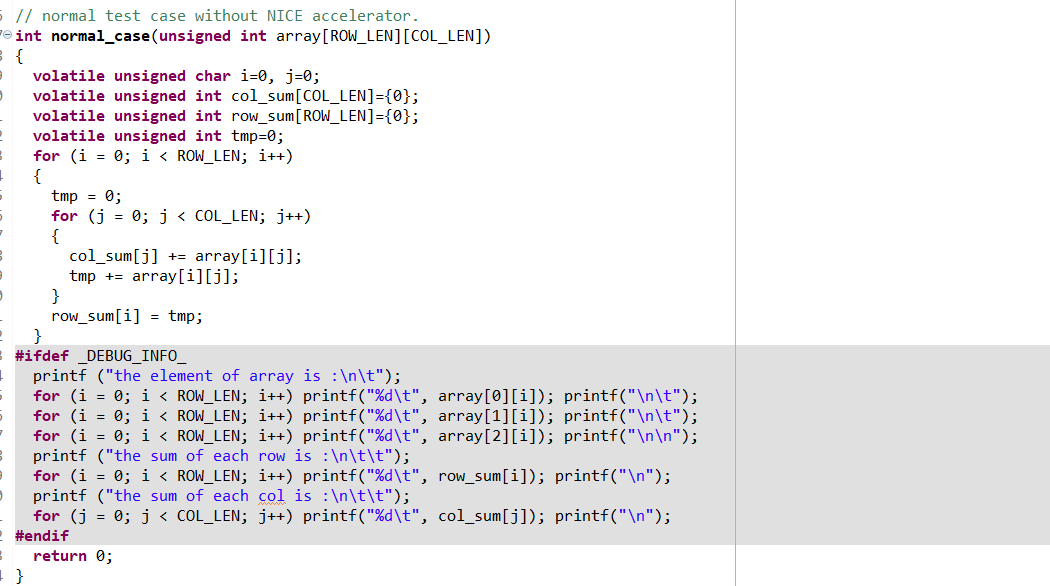

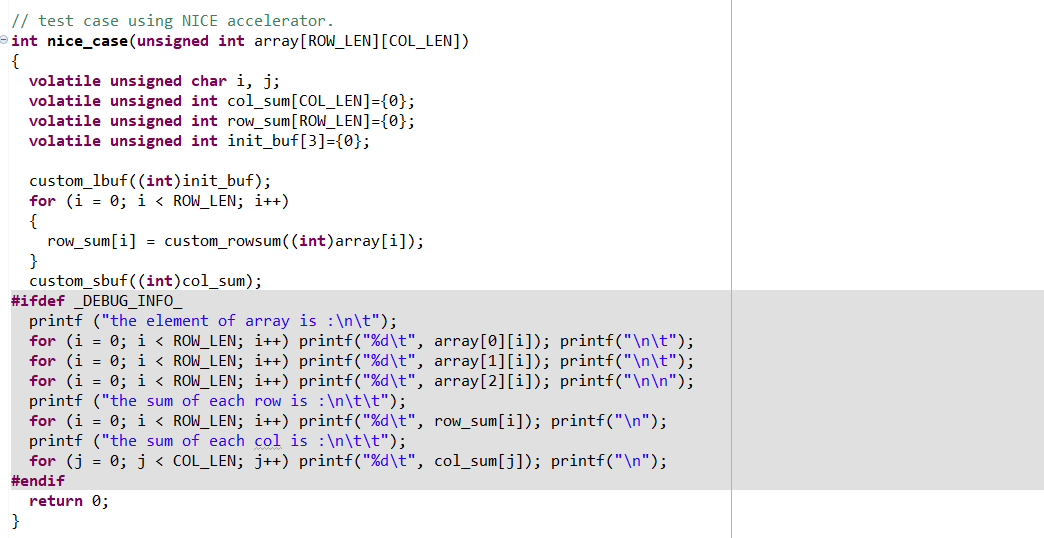

欸,想看看运算结果,怎么没有呢?让我去看官方给的nice_demo.c的主函数,normal_case和nice_case函数分别如下图

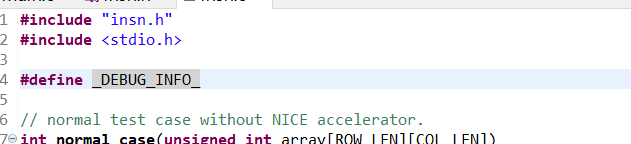

可以看到,输出运算结果的pritnf函数被#ifdef所定义,所以我们如果想在VIVADO的控制台看到输出结果,要先在main.c中定义DEBUG_INFO,如下图

这样,将编译后生成的.verilog文件再用VIVADO读入仿真,可以看到了运算结果如下