谷歌发布了KataOS,这是一种针对开源RISC-V芯片上嵌入式系统的新的安全操作系统的早期探索。

谷歌的KataOS“几乎完全用Rust编写”,这是Android开源项目和Linux内核项目采用的编程语言。「谷歌发布了用Rust编写的开源安全操作系统KataOS」https://www.zdnet.com/article/google-shows-off-kataos-a-secure-operating-system-written-in-rust/——ZDNet

最新Ubuntu 22.10的版本已宣布正式发布。这次有很多新功能,其中包括对RISC-V的支持.

「Ubuntu 22.10发布了改进的Steam应用程序,支持RISC-V」https://www.tomshardware.com/news/ubuntu-22-10-released

Andes宣布推出N25F-SE处理器,这是全球首款符合ISO26262 ASIL-B标准的RISC-V CPU IP。Andes表示,所有可配置选项都经过了全面认证,因此芯片设计团队不受一个固定CPU配置的限制。

「Andes推出首款符合ISO 26262标准的IS CPU IP,计划推出DSP版本」

https://www.eenewseurope.com/en/andes-claims-first-risc-v-cpu-ip-with-full-iso-26262-compliance-plans-dsp-version/

——EENews

从RISC-V指令集的诞生到现在已经历了10多个年头。国内的企业和科研机构也已从最开始的观望逐渐转变为主动接纳和积极推动这一新的开放体系架构。秉承去年第一届专题的初衷,今年我们再一次组织RISC-V技术及生态的研讨,记录、探讨和推广国内产业和学术界在RISC-V相关问题上的最新进展和贡献。本专题主要面向RISC-V软硬件相关的研究人员和工程人员,内容涵盖了体系结构、安全、编译器、自动化测试、嵌入式应用等领域,反映了我国学者在相关领域的最新研究进展。

「专题 | RISC-V技术及生态」

https://mp.weixin.qq.com/s/xJ7Fl26x9xn4bUuFbiPhsQ

——计算机系统应用微站

将Arm® CPU设备(电路板和软件)上开发的应用程序轻松快速地移植到RISC-V CPU设备,这一任务颇具挑战性。那么,跨不同CPU开发应用程序时面临哪些挑战?

「跨Arm®和RISC-V CPU轻松迁移应用程序」

http://www.eepw.com.cn/zhuanlan/269282.html

图片:RZ/G2UL和RZ/Five引脚兼容性和软件配置图

来源:EEPW

——EEPW

国芯科技10月24日在互动平台表示,公司于2017年开始投入基于RISC-V指令集的CPU核和软件工具链的开发,目前已完成CRV0、CRV4L和CRV4E等CPU核以及相应的软件集成开发工具的开发。公司CRV0及CRV4系列 等RISC-V指令集CPU能够达到ARM Cortex M0 及Cortex M4等CPU核心性能指标,满足未来的替代需求。公司未来将进一步投入RISC-V指令集CPU技术研发,形成系列化的RISC-V指令集的嵌入式CPU,在公司现有安全产品的基础上支持生物特征识别、汽车电子、工业计算及人工智能的拓展功能,以实现RISC-V指令集CPU对物联网节点、金融安全、端安全以及汽车电子与工业控制应用芯片产品的全面覆盖。

「国芯科技:将进一步投入RISC-V指令集CPU技术研发,形成系列化RISC-V指令集嵌入式CPU」https://baijiahao.baidu.com/s?id=1747553726042430824

北京君正10月25日披露投资者关系活动记录表显示,公司实际过去几年一直在进行RISC-VCPU的研发,到目前为止公司已经基本完成了一款公司命名为V2的CPU内核的研发,这款相对来讲是一颗中等性能的内核,与ARM的A53系列相当。公司预计从明年开始T系列、X系列、C系列,都能够逐步从MIPS的XBurst系列转到V系列内核,这个V系列完全兼容RISCV,在性能、功耗、指令密度等方面还是比较有优势的,所以公司的RISCV已经基本准备好了,明年开始会陆续亮相在新的产品中。

「北京君正:RISCV已基本准备好,明年开始会陆续亮相在新产品中」

https://new.qq.com/rain/a/20221026A03YWH00

——腾讯网

芯来科技助力裕太微电子推出力作——高性能以太网L2 Lite-Managed YT9215系列交换芯片。该系列产品拥有完全自主知识产权。产品兼容2.5G/1000M/100M/10M等多种端口速率、支持线速交换。其功能、性能等各方面指标均达到世界先进水平。

该系列产品均内置芯来科技RISC-V N205处理器内核。

10月21日消息, 嵌入式开发软件和服务的全球领导者IAR Systems宣布持续为SiFive的RISC-V车用CPU IP提供解决方案:IAR Systems旗下的IAR Embedded Workbench for RISC-V支持最新的SiFive车用E6-A和S7-A产品系列,以满足信息娱乐、连接和ADAS等汽车应用的需求。IAR的完整开发工具链帮助OEM和供应商的嵌入式软件开发人员充分利用RISC-V提供的能效、简单性、安全性和灵活性。

「IAR Systems RISC-V功能安全版开发工具为SiFive车用E6-A和S7-A产品提供支持」https://baijiahao.baidu.com/s?id=1747285077559296640&wfr=spider&for=pc

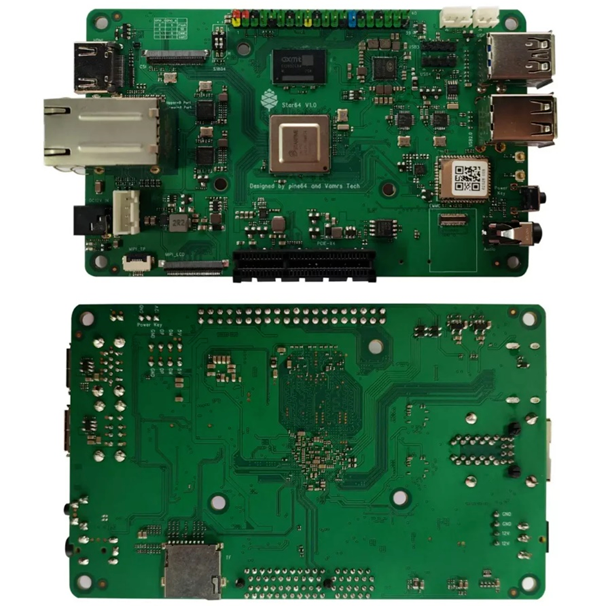

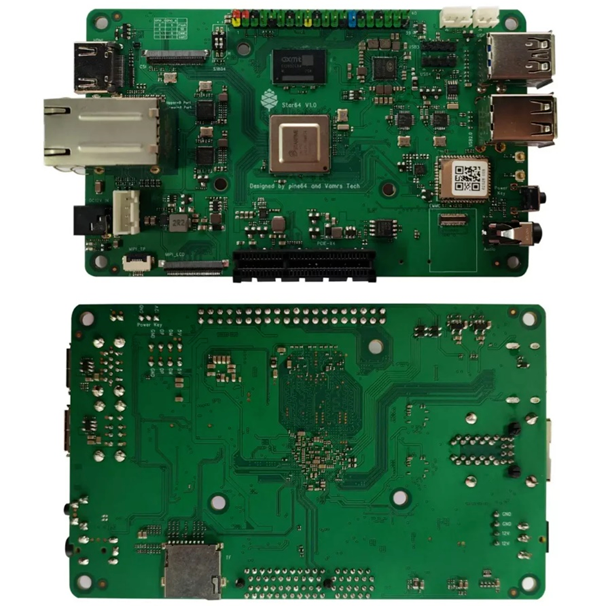

全球知名开源硬件厂商Pine64推出全新RISC-V单板计算机——Star64,搭载赛昉科技新一代量产多媒体处理器昉·惊鸿7110 SoC(JH7110)。

JH7110采用成熟的台积电28nm工艺,搭载64位高性能四核RISC-V CPU,工作频率1.5GHz,2MB的二级缓存。JH7110集成3DGPU、H.264/H.265视频编解码IP及ISP IP,是一款功能强大的多媒体处理平台。「Pine64推出全新RISC-V单板计算机,搭载赛昉JH7110 SoC」

Red Semiconductor Ltd. 是一家英国初创公司,设计基于Open Power处理器指令集架构的“auditable”微处理器系列。

该公司董事长David Calderwood表示,该处理器旨在运行 Linux 操作系统等,并且能够在本机模式下运行x86代码,这要归功于仿真功能。「RISC-V有局限性,英国芯片初创公司,选择了Open Power」

为促进集创赛青年学子之间的技术交流,集创赛最新推出集成电路青年论坛。论坛由工信部人才交流中心主办,北京智芯国信科技有限公司运营,将以线上技术分享为主要形式,全年组织多个学术交流系列。

拟邀请数支第五届、第六届集创赛“芯来RISC-V”杯优秀团队进行作品分享与开源,杯赛作品主要是围绕开源蜂鸟处理器进行扩展设计,构建面向专用应用领域(譬如人工智能、信息安全、工业控制等)的SoC,进而完成实际的应用系统开发。

2022年10月18日全球领先的高集成度、低功耗图像处理SoC芯片公司六角形半导体有限公司(以下简称“六角形半导体”)宣布,基于自研RISC-V核开发的图像处理SoC芯片累计出货超千万颗,应用覆盖手机超高清视频编解码系统处理、智慧家电、车载中控、工业控制等各类智能终端人机交互显示控制。

「自研RISC-V核,六角形半导体开发图像处理SoC芯片出货超千万颗」https://baijiahao.baidu.com/s?id=1746926879257298649&wfr=spider&for=pc

https://interestingengineering.com/innovation/rise-of-risc-v-the-computer-chip——Interesting Engineering

https://mp.weixin.qq.com/s/7Lmx4hMq9Zm30-jkuNqv6g

OpenArkCompiler Weekly(第135期·2022-10-23):https://zhuanlan.zhihu.com/p/576446767

OSTD Weekly (第173期·2022-10-26):https://mp.weixin.qq.com/s/QPSng7H_UVhMBj_WoK-BaQ

RISC-V Linux内核及周边技术动态(第17期·2022-10-26):

https://mp.weixin.qq.com/s/wuTeB-xsZM06BEwQhY0DuQ

更多实验例程

www.rvmcu.com