近日,深度数智在第十届开源操作系统年度技术会议上,正式发布了全球首款RISC-V开发笔记本电脑ROMA,并默认搭载openKylin(开放麒麟)国产操作系统。「全球首款RISC-V笔记本电脑ROMA正式发布,搭载国产操作系统」https://www.ednchina.com/news/a11084.html

图片来源:电子技术设计

本周,英国方面传来消息,ARM已经就改变商业许可费收取模式一事和高通、小米、联发科、紫光展锐等公司接洽,但结果并不理想。

「对小米/高通等无情涨价 一些厂商已考虑弃用ARM芯片:RISC-V的机会来了」瑞萨为想要基于RISC-V指令集架构进行新设计的开发人员推出了微处理器选项。瑞萨RZ/Five系列MPU提供由一组丰富的存储器和通信接口支持的RISC-V方案。RZ/Five RISC-V CPU内核是一个单核AX45MP,运行时钟频率高达1GHz。MPU还为高速DDR3L或DDR4-1600 DRAM提供16位接口。「瑞萨基于RISC-V的新款MPU为高性能网关应用提供快速接口」

3月16日,中国移动OneOS与紫光展锐合作的智能穿戴项目首批产品完成产线生产,预期年出货量300万台,迈出了国产芯片和操作系统融合关键性的一步。芯片方面,为避免受国外ARM架构的授权约束,中国移动基于开源开放的RISC-V进行技术攻关,目前已推出多款物联网芯片,关键指标达到国际领先水平。2022年12月,中国移动集团首席专家肖青在中国移动全球合作伙伴大会上发布首款RISC-V内核NB-IoT和LTE Cat.1bis通信芯片。其中,NB-IoT通信芯片休眠功耗达到业内最低,平均低于800nA,接收灵敏度业内最优,平均小于-118dBm,与MCU芯片共同入选国资委《中央企业科技创新成果推荐目录(2022年版)》。目前相关芯片已完成自研物联网操作系统OneOS、开源鸿蒙OpenHarmony Lite OS的移植适配。「中国移动打造硬核科技,加快物联网操作系统与芯片融合发展」http://www.cctime.com/html/2023-3-29/1647291.htm

图片来源:飞象网

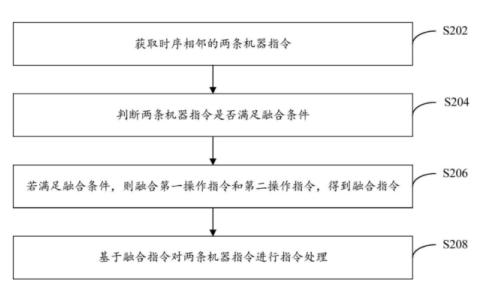

集微网消息,面对美国的制裁,阿里巴巴持续加大对RISC-V的投入,其芯片部门平头哥一直在加速RISC-V芯片架构在中国的商业应用。平头哥的RISC-V专利,通过对多条指令进行融合,从而在不增加指令的情况下,实现硬件加速,提升处理器核的性能。并且,因为没有增加额外的指令,也避免了与已有的处理器指令系统兼容性差的问题。「「专利解密」平头哥最新RISC-V指令融合专利」指令融合方法的步骤流程图

图片来源:集微网

在IIC上海期间,旋智科技发布了一款应用于汽车直流无刷有刷电机的内置N-FET预驱微控制器。旋智科技前身为仙童半导体公司的电机产品线事业部,于2014年通过管理层剥离开始独立运营。旋智目前的电机控制器产品类别并不很多,但仍选用了两种内核。现有的32位的M3和M4F内核主要面对算力需求在240MHz以内的电机控制应用,而64位的RISC-V内核则更多面向算力需求在400MHz以上的工业场景。目前公司开发的高性能64位RISC-V内核主要面向高性能伺服控制应用,其RISC-V内核性能对标并优于ARM Cortex R5F内核。「满足现有汽车低压12V直流无刷/有刷电机驱动需求,技术布局48V未来」https://www.esmchina.com/news/10178.html

图片来源:国际电子商情

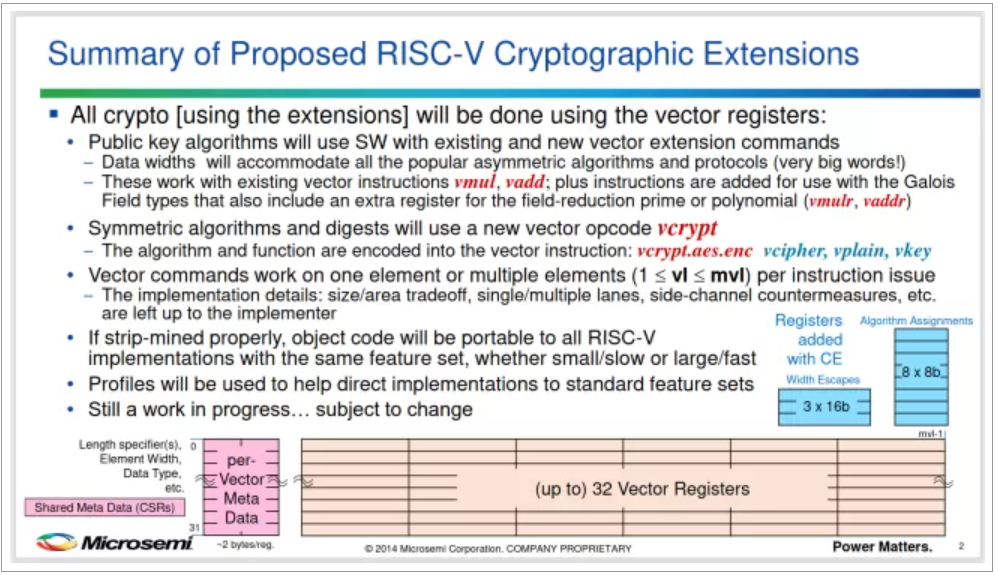

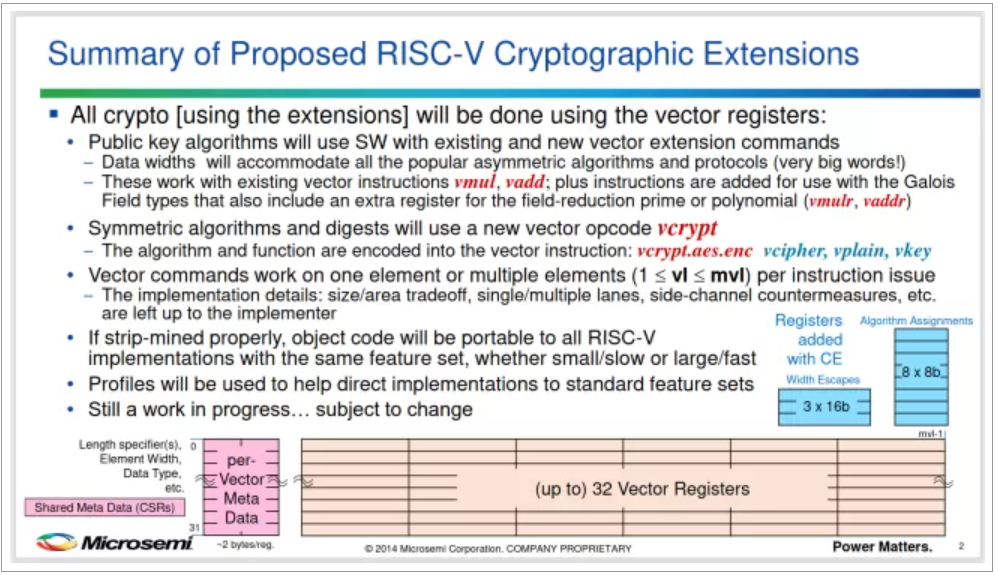

国芯科技基于自主可控CRV0 CPU内核研发的CCM3310S-L、CCM3310S-LP安全芯片已规模化应用于智能穿戴eSIM、版权保护、智能门锁安全、ETC OBE-SAM、燃气表安全SE和直播星SE等物联网应用领域。上述RISC-V安全芯片均采用40nm EFlash工艺设计,内置高安全防护机制,支持DES、AES、RSA、ECC、SHA等国际算法,SM2、SM3、SM4等国密算法,安全等级达到国家密码管理局商用密码检测中心《安全芯片密码检测准则》第二级要求。芯片具备高安全性、超低功耗和小尺寸等特点,出货量已达数百万颗。「国芯科技基于RISC-V CPU的安全芯片获得多领域规模化应用」LLVM 17首次支持RISC-V矢量加密扩展ISA。最新的LLVM 17 Git代码首次支持向量加密扩展ISA的v0.3草案规范,该规范旨在加速未来RISC-V处理器上的加密操作。这些说明是由SiFive的Brandon Wu开发的。https://www.phoronix.com/news/LLVM-17-RISC-V-Vector-Crypto

图片来源:phoronix

Imperas Software已与MIPS和Ashling签署了一项三方合作协议,涵盖RISC-V软件开发的各个方面。三者将使用MIPS eVocore P8700 RISC-V多处理器的Imperas参考模型,以及Ashling的RiscFree SDK工具,把对开发人员的支持级别从硅验证前期扩展到原型阶段,再扩展到最终用户。在2023全球嵌入式大会上Codasip CCO表示,差异化是成功的关键,根据特定工作量定制硬件是创新的唯一途径。自定义计算并不是什么新鲜事——如今在移动或汽车行业都有领先的参考文献。正是开放的RISC-V架构和高质量处理器IP的结合带来了这种创新可能性。「2023全球嵌入式大会:是时候让定制计算来适配万物了」https://semiengineering.com/embedded-world-2023-its-time-to-architect-all-ambitions-with-custom-compute/

图片来源:Semiconductor Engineering

——Semiconductor Engineering

2000年左右EDA行业仕途定义一个更高级别的抽象系统ESL来处理软硬件协同。ESL试图通过考虑应该在软件中执行什么,在哪个处理器上执行什么,或者需要在硬件中执行什么来实现性能目标,以及如何连接它们来定义最佳芯片设计。事实证明,这在当时是一项过于复杂的任务,而且提供的好处太少。有了RISC-V,许多人有了更严格的目标。如何优化处理器核心以执行特定任务。通过适当的ESL,与使用标准组件或IP和优化实施所能实现的目标相比,他们可以将整体指标(无论是面积、速度、功率还是它们的组合)提高几个数量级。——Semiconductor Engineering

Jim Keller究竟在做什么芯片?

https://mp.weixin.qq.com/s/K0GhV_eV6tX80Gyma4bhFw

OpenArkCompiler Weekly(第155期·2023-03-27)

https://zhuanlan.zhihu.com/p/617276953

开源开发工具周报OSDT Weekly(第194期·2023-3-22)