团队编号:CICC1849

团队名称:能用就行队

学校:安徽工业大学

团队成员:高志强,叶颖,汪志泉

指导老师:王玲玲解决:为解决蜂鸟e203移植A7lite-100T时时钟信号与复位信号不一致,IP核出现未知情况。

第一步:

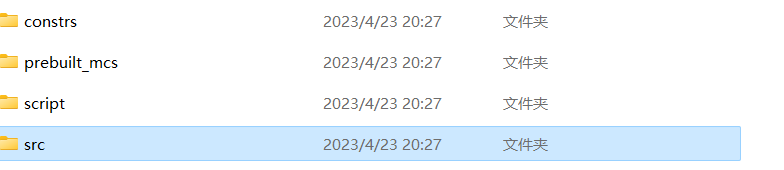

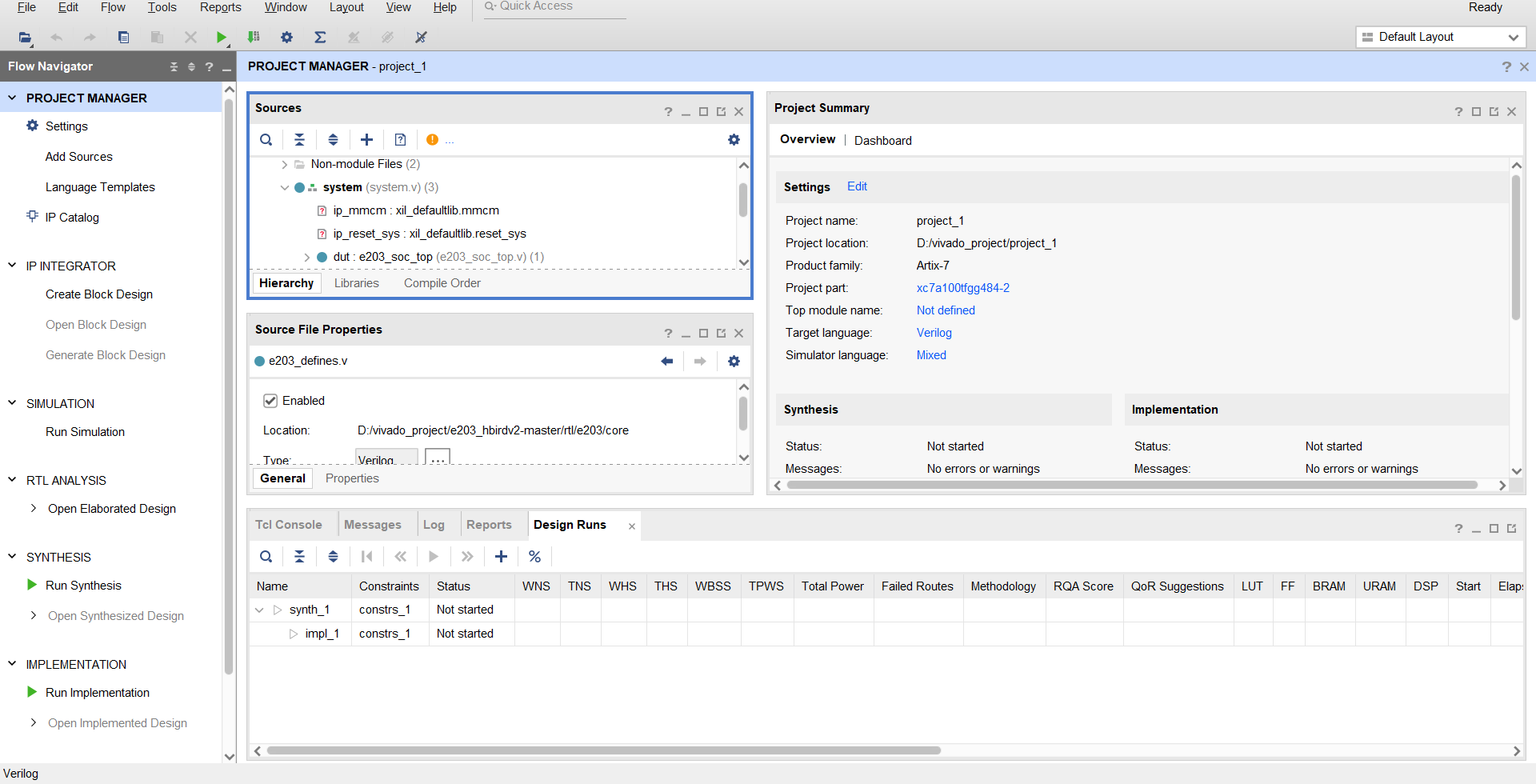

我们要来创建了一个Vivado的工程,是我们进行仿真的第一步。将蜂鸟e203的基础代码:提供的e203添加进去,并加入ddr200T中的

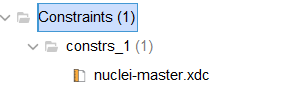

src.文件中的system.v文件并加入约束文件(constrs文件夹之中)

第二步:

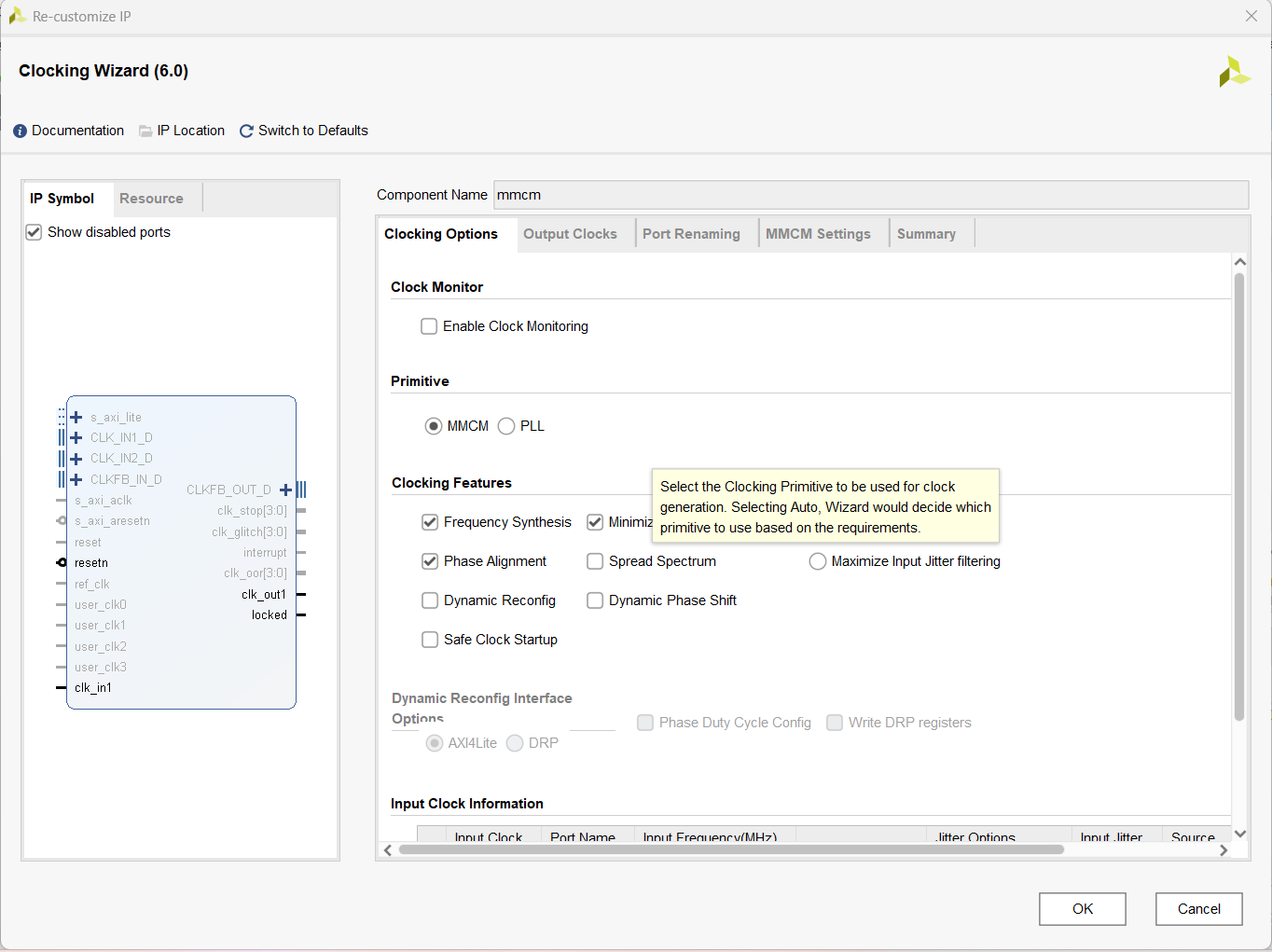

修改顶层文件更改system.v文件,system.v是基于蜂鸟官方的开发板mcu200T或者ddr200T来生成的.这两块开发板上有两路输入时钟100Mhz和32768Khz,其中100Mhz用于分频为16Mhz为cpu提供核内运行时钟,32768Khz为常开域时钟.而我们的A7lite-100T开发板上只有一个50Mhz输入时钟,因此需要在顶层模块中例化MMCM(可以在建立vivado工程时再例化)来产生上述两个时钟添加clk_div.v文件

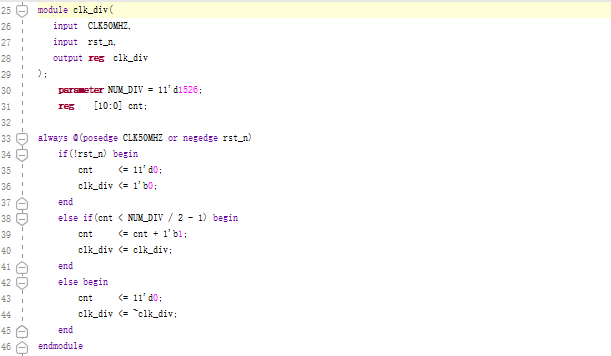

代码如下:

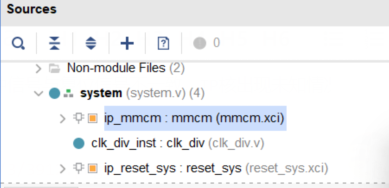

可以发现clk_div.v文件与system.v文件的IP核相匹配。

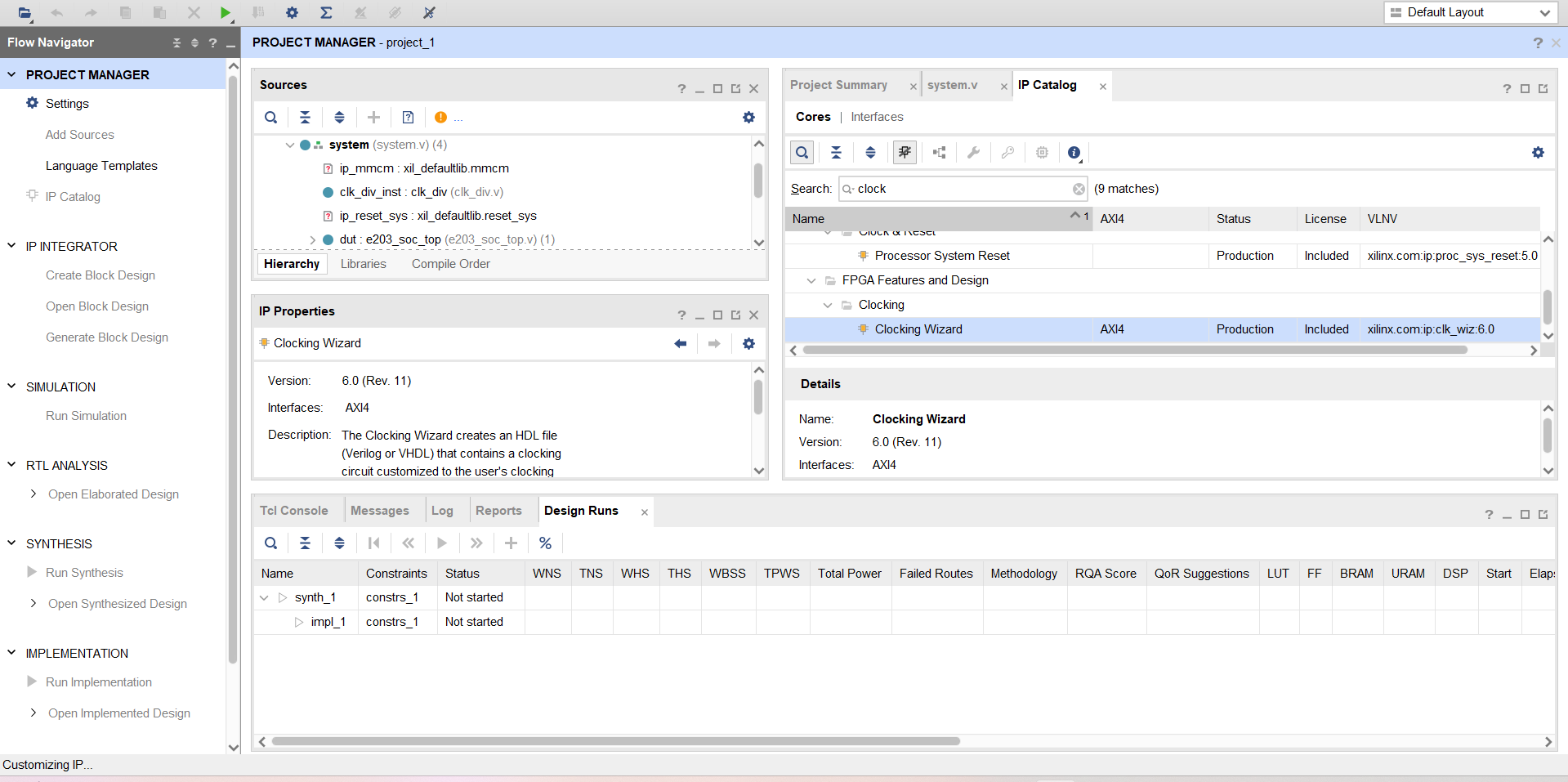

第三步:

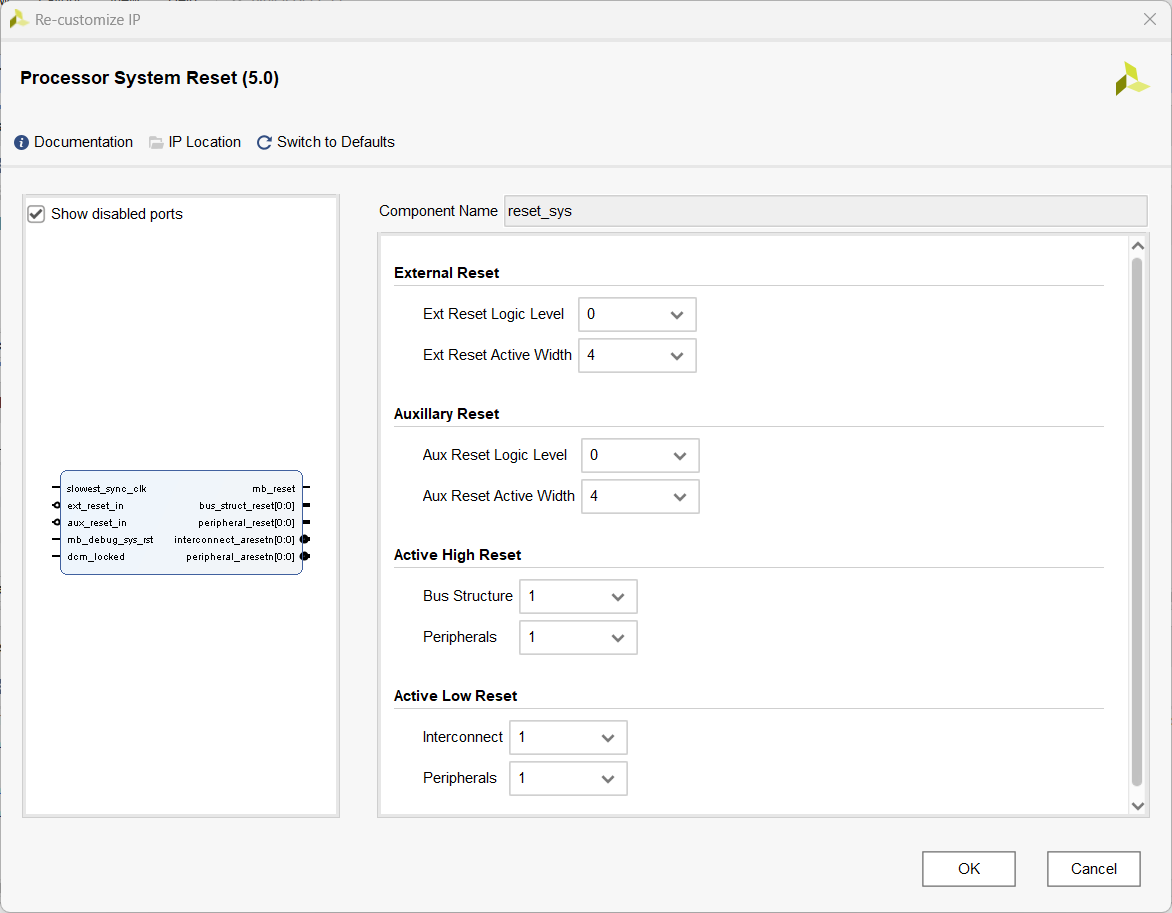

打开IP catalog,为时钟与复位信号添加IP核,可以搜索自己所需要的IP核,并调节参数,以该例子为例。

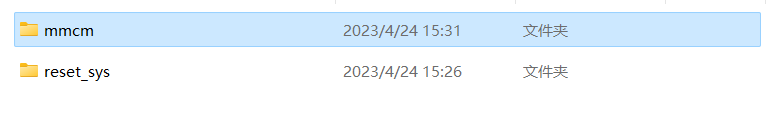

工程创建中文件夹中则会出现下图的IP文件:

第四步:

开始分析与更新,并观察到IP核已经变化符号后进行编译分析,以确保IP核的正确性。

第五步:

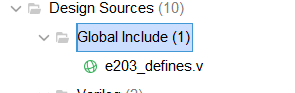

将e203_defines.v文件type变为Verilog header类型,并且将e203_defines.v文件改为全局文件Global Include:

第六步:将上述的约束文件变更为自己所需要的约束规则。

最后:

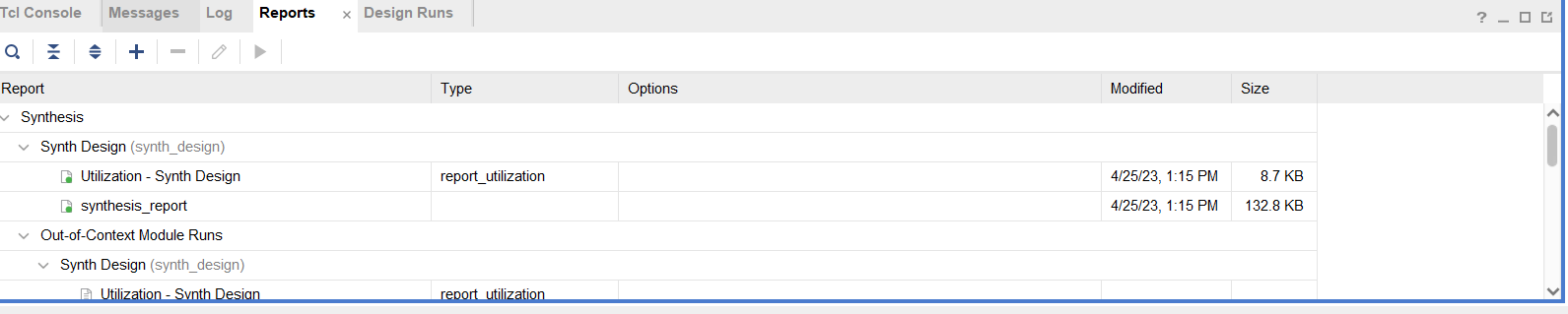

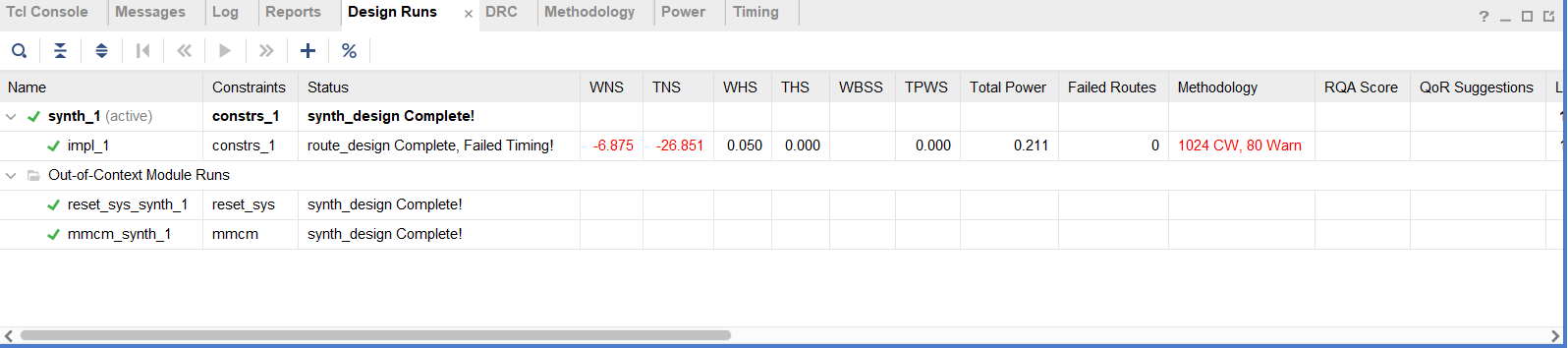

分析综合,将高级抽象层次的电路描述转化为较低层次的描述

下图为综合报告:

完成布局布线:

至此,我们已经完成并解决了蜂鸟e203移植到A7lite的相关问题