报名编号:CICC6258

团队名称:芯真累啊

环境:vivado2019.2

下载E203源码地址:https://github.com/riscv-mcu/e203_hbirdv2

0、准备文件:

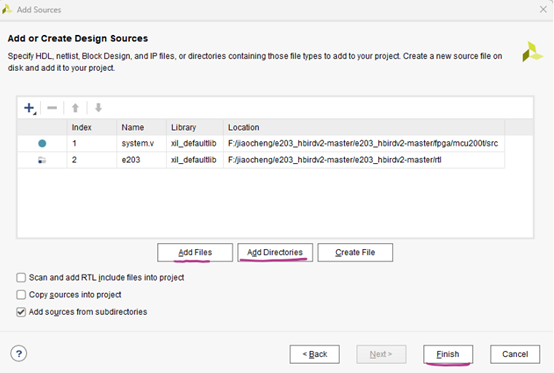

(1)System文件

地址:e203_hbirdv2-master/e203_hbirdv2-master/fpga/mcu200t/src/system.v

(这里我们选用的是mcu200t芯片,若先用其他芯片可用其他system文件替代)

(2)rtl文件

地址:e203_hbirdv2-master/e203_hbirdv2-master/rtl/e203

它的文件夹内部为

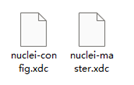

(3)约束文件

地址: e203_hbirdv2-master/e203_hbirdv2-master/fpga/mcu200t/constrs

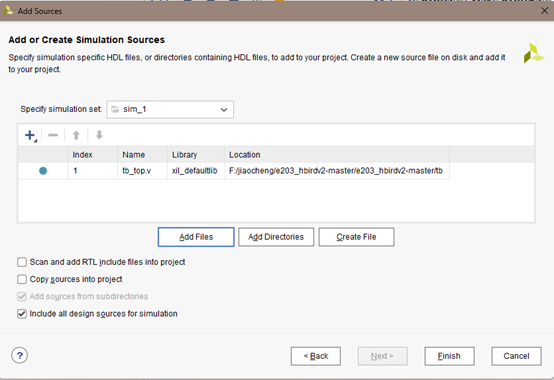

(4)tb_top.v 文件

地址:e203_hbirdv2-master/e203_hbirdv2-master/tb/tb_top.v

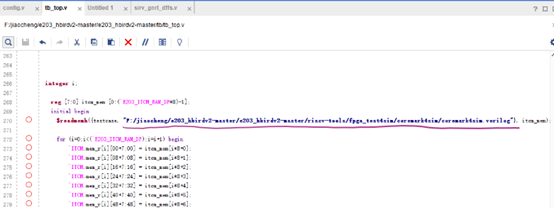

(5)benchmark文件

地址:

e203_hbirdv2-master/e203_hbirdv2-master/riscv-tools/fpga_test4sim/coremark4sim/coremark4sim.verilog

e203_hbirdv2-mastere203_hbirdv2-masterriscv-toolsfpga_test4simdhrystone4simdhrystone4sim.verilog

hbird master文件中提供了dhrystone和coremark 2种benchmark工具。若有其他benchmark工具需求,可以自行下载并转换为.verilog文件。

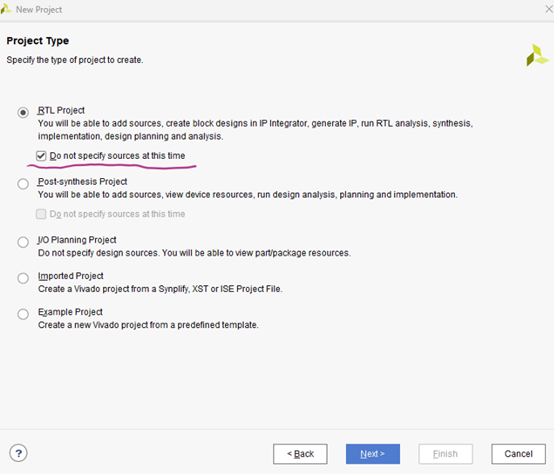

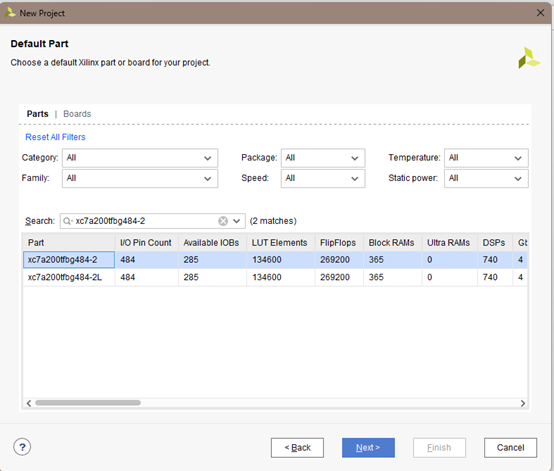

这里由于我们选用的是MCU200t,故选择xc7a200tfbg484-2的FPGA核心。

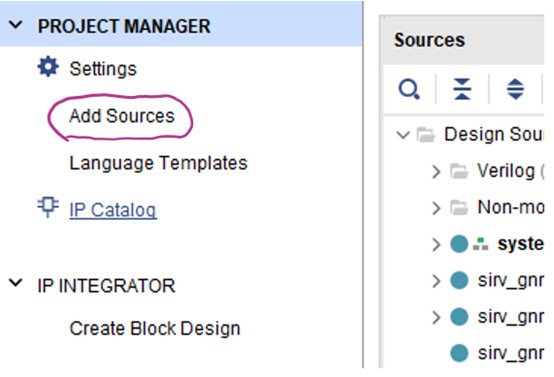

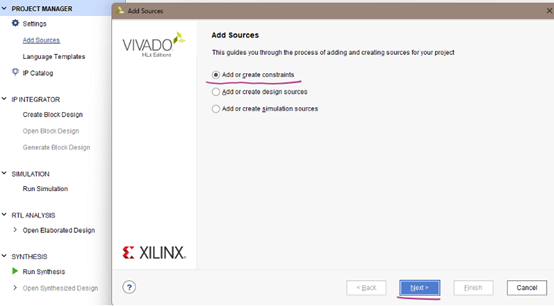

add files:system.v

add directories:e203

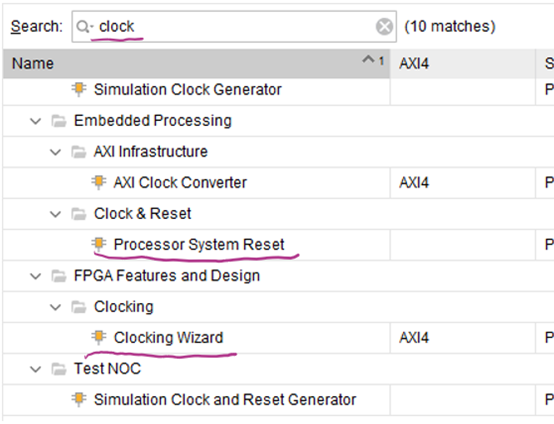

分别找到Clocking Wizard和Processor System Reset

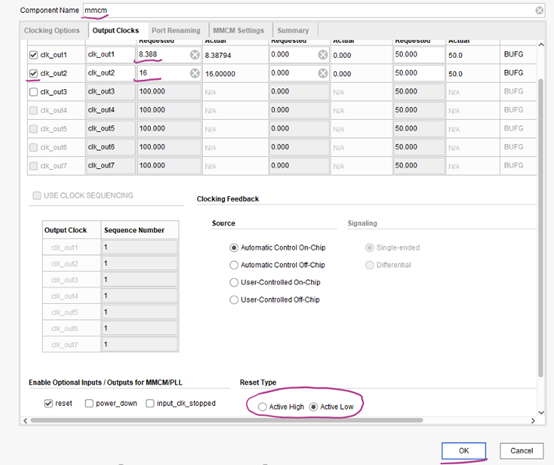

Processing Wizard:

命名为mmcm,clk_out1,clk_out2的requested改为8.388和16,下降沿触发

Processor System Reset改名为reset_sys

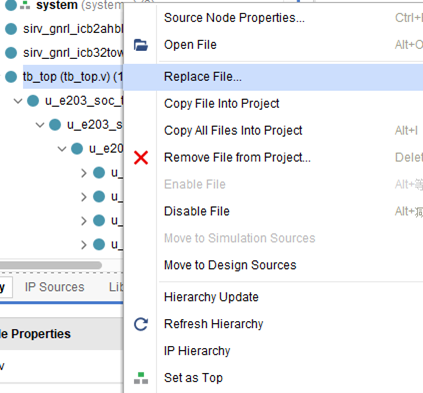

e203_defines.v右键,设为global,以及file type 改为Verilog Header

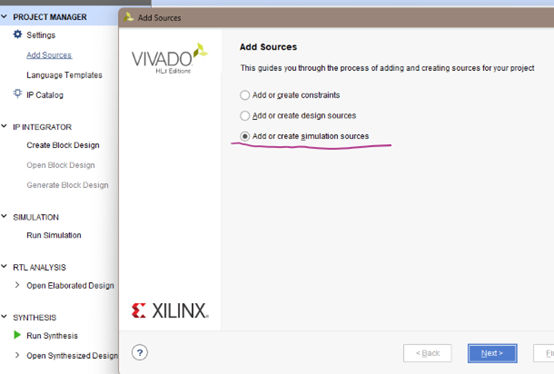

在simulation source中找到tb_top.v文件。右键,set as top

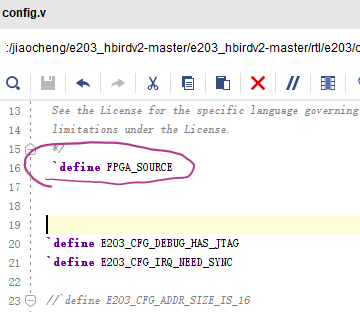

在config.v中添加一句

将tb_top.v中readme读取的文件地址设为存储testbench的.verilog文件的地址,这里进行的是Coremarkpao’fen记得把””改为”/“。

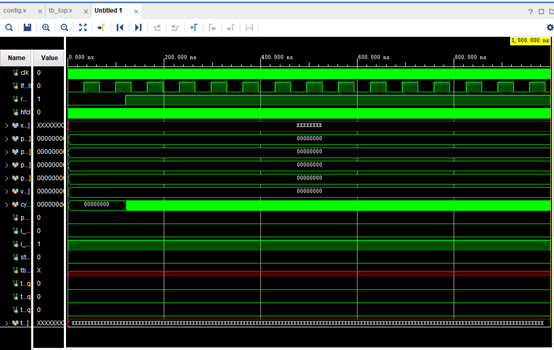

得到行为级仿真的结果如下:

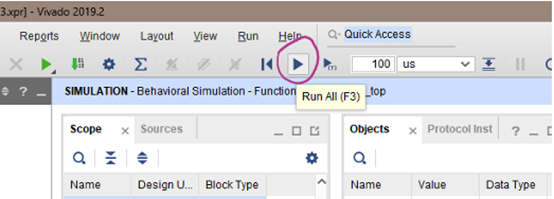

run all

开始运行跑分程序,此时TCL console信息栏中可以看到benchmark运行的实时情况。

等待约10分钟左右后,得到coremark跑分情况。

参考文章:

Vivado 蜂鸟 e203 MCU200T/DDR200T 逻辑综合 RISC-V 详细教程蜂鸟e203导入vivado并扩展ip核_Jie_MSD的博客-CSDN博客

【竞赛分享】利用vivado实现对e200_opensource 蜂鸟E203一代的仿真全国大学生集成电路创新创业大赛_RISC-V论坛讨论_RISC-V MCU中文社区 (rvmcu.com)

手把手教你移植蜂鸟E203 hbridv2【集创芯来RISC-V杯】 - 简书 (jianshu.com)