团队编号:CICC1413

团队名称:“芯”之所向

在添加浮点运算单元时,可以引用开源的浮点运算器以简化所需工作任务压力。在此我们采用了FPnew这个开源工程,再次介绍一些如何将其导成vivado工程。

首先在github上下载fpnew工程文件,解压到相应路径。

https://github.com/openhwgroup/cvfpu/tree/c15c54887b3bc6d0965606c487e9f1bf43237e45

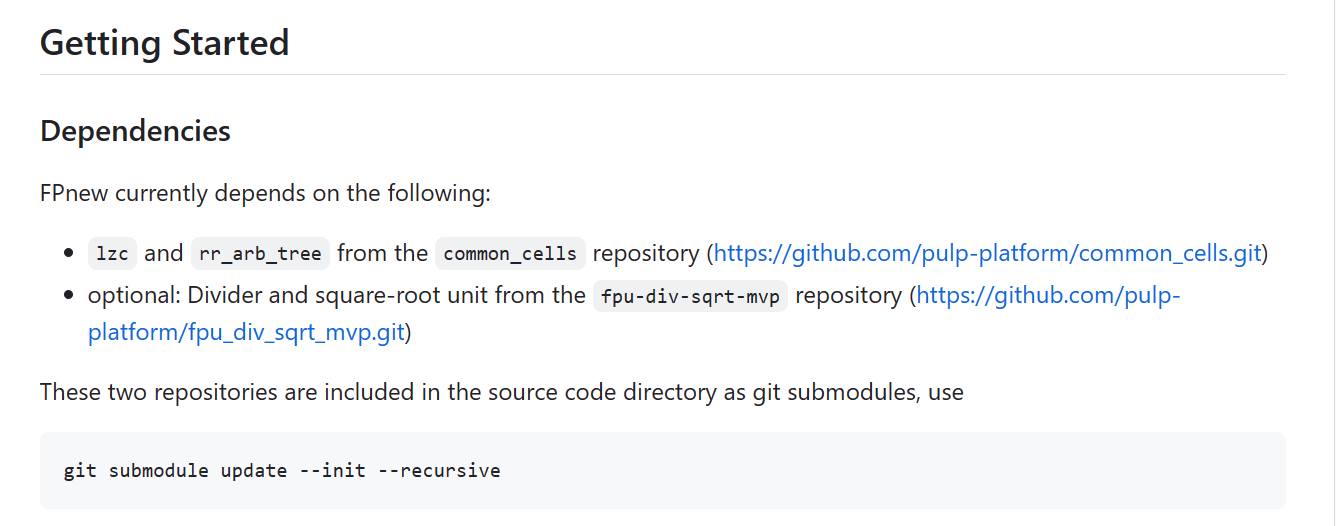

根据其中README.md得知如果运行该工程需要添加两个依赖包。如下图所示。

进入其给出的网站将依赖包下载完毕即可。

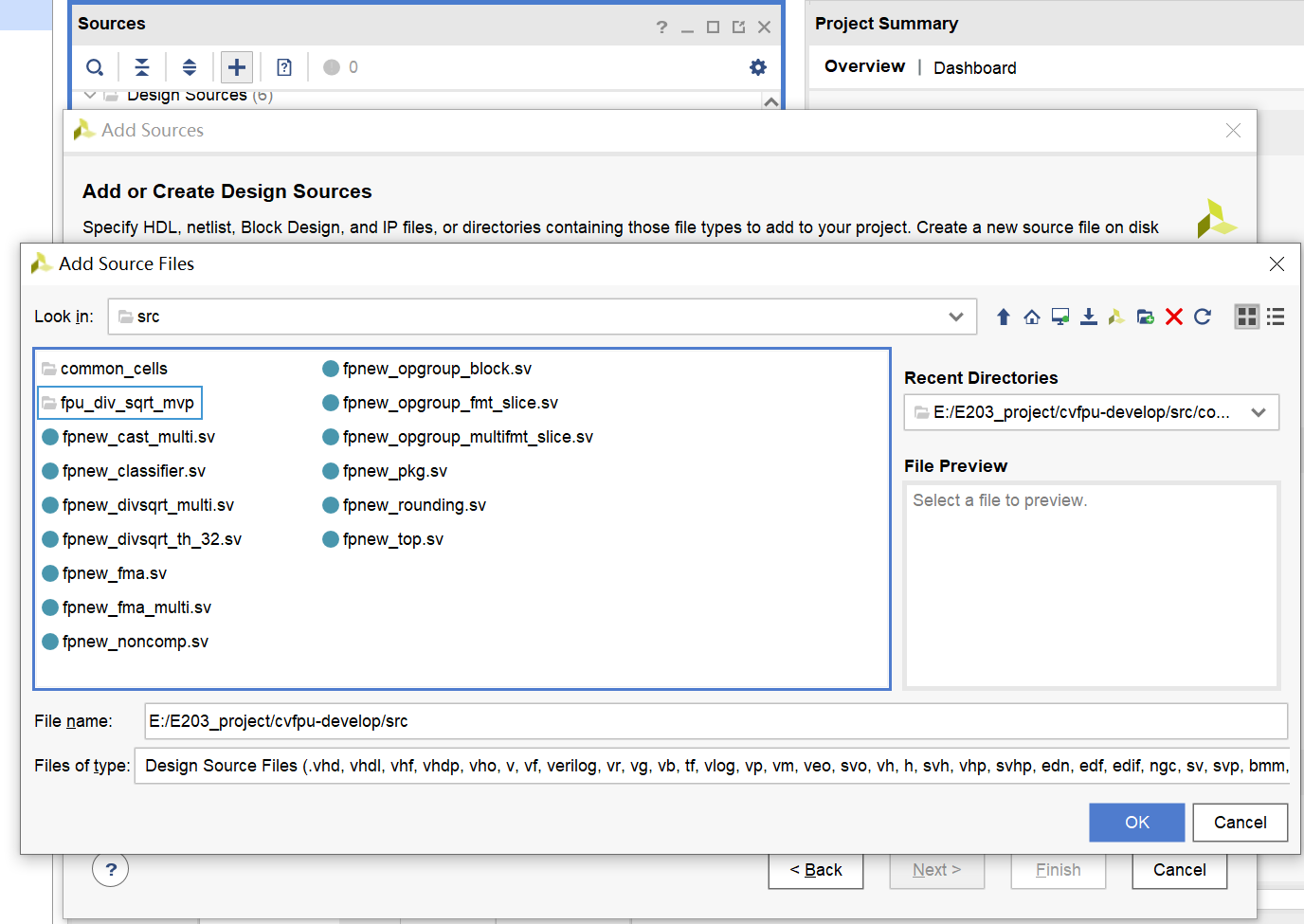

打开vivado,点击File->Project->New创建新工程,点击Sources上的“+”号添加工程文件,将cvfpu-develop\src目录下的所有.sv文件添加进工程。

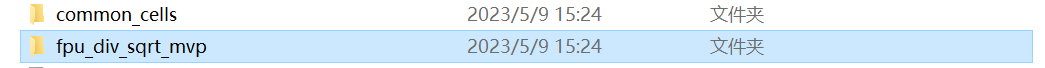

在该目录下我们可以看到有两个文件夹common_cells和fpu_div_sqrt_mvp。这两个文件夹目前处于空的状态,只要将刚刚下载好的依赖包添加进去即可。

下载下来的fpu_div_sqrt_mvp-master依赖包中文件全部放在fpu_div_sqrt_mvp中,common_cells-master依赖包中文件放在common_cells中。此时注意,将common_cells-master\include\common_cells路径下的registers.svh移动到common_cells文件夹中,因为该文件为头文件,文件引用时的路径在此路径中。

将fpu_div_sqrt_mvp\hdl目录下的.sv、common_cells\registers.svh以及common_cells\src\rr_arb_tree.sv文件添加进工程,并将registers.svh文件设置为头文件即可。

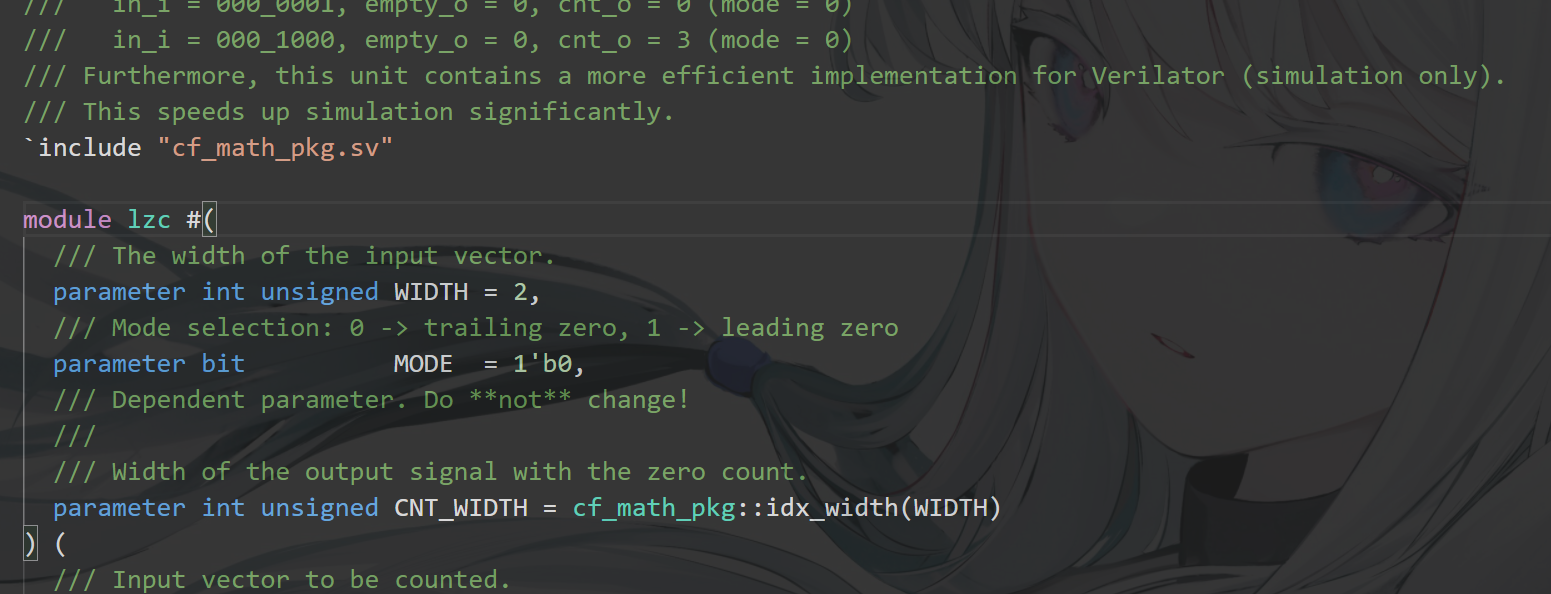

此时找到lzc.sv文件,在模块前面加`include “cf_math_pkg.sv”

此时,便可以成功综合工程了。