喜欢3次

团队编号:CICC1156

团队名称:兔飞猛进

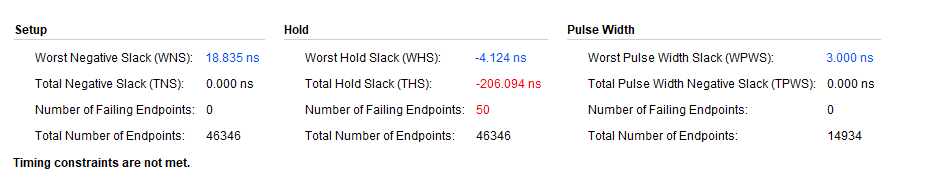

1、将 nuclei-config.xdc 和 nuclei-master.xdc 加入到项目工程中,综合得到时序约束报告如下:

保持时间约束不满足,分析原因,发现所有不满足均出现在 clk_out1_mmcm 和 sys_clk_pin 这两个时钟上:

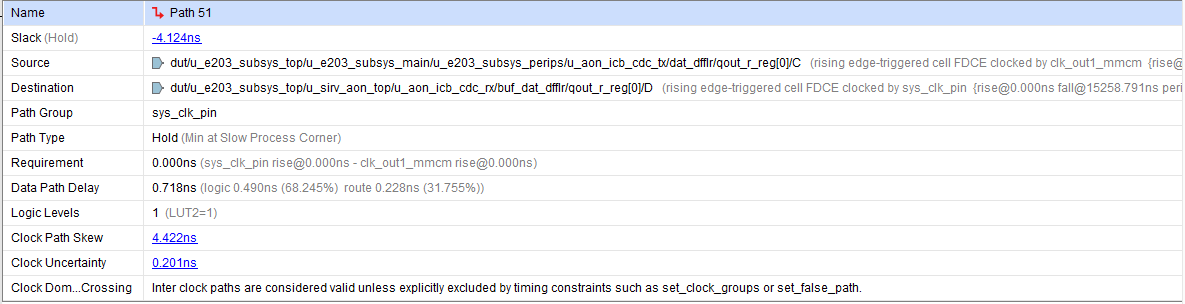

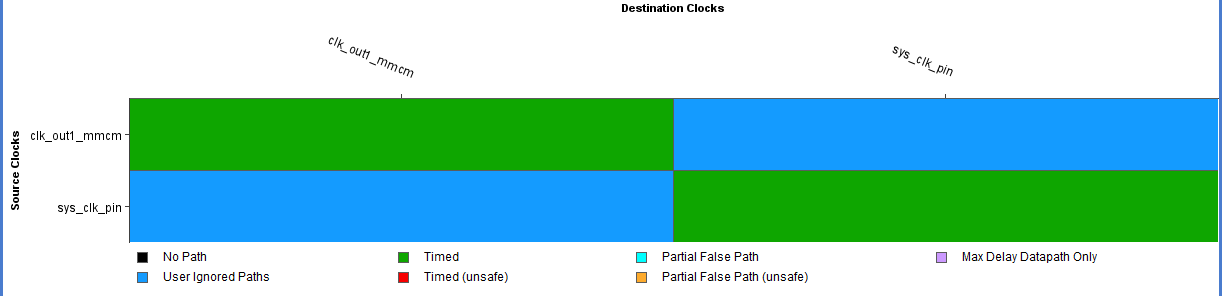

2、基于上述问题,运行 synthesis 中的 report clock interaction 得到以下结果:

图中的红色标记代表两个时钟是没有约束的异步时钟

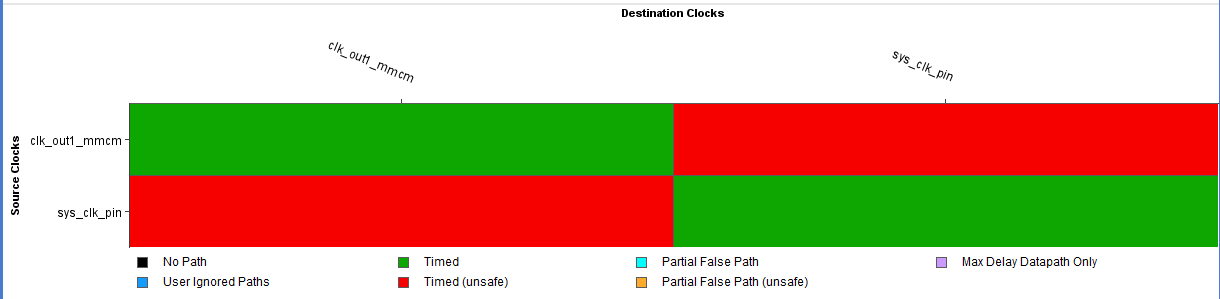

3、在 synthesis 中 打开 edit timing constraints 设置异步时钟,如下图:

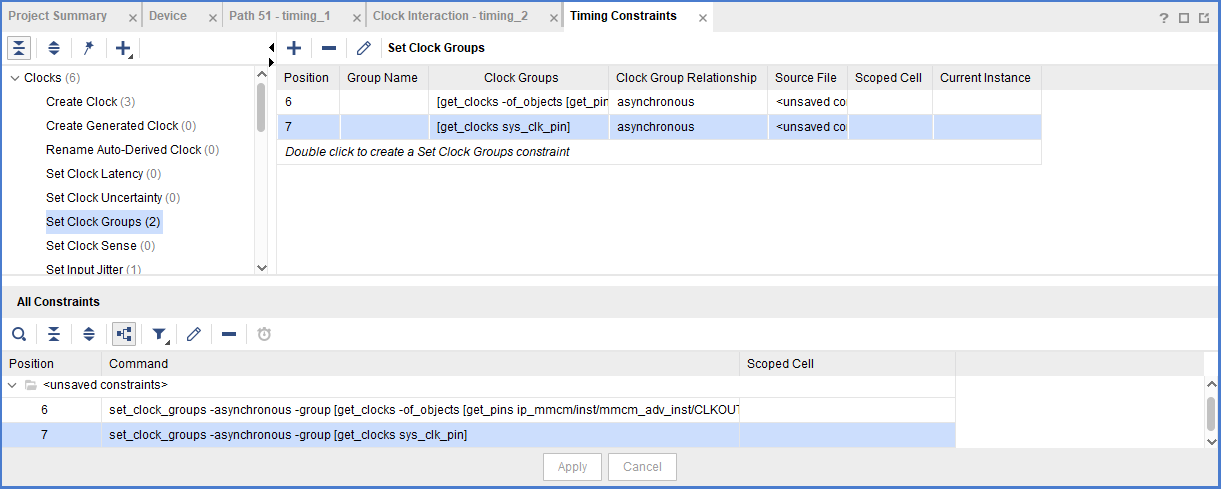

4、再重新运行 synthesis 中的 report clock interaction,得到以下结果:

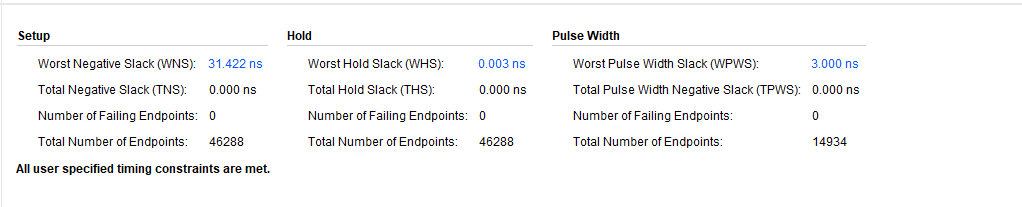

5、异步时钟设置完成后,再重新综合得到时序报告如下:

时序约束满足了。