报名编号:CICC2353

称团队名:不划水队

所选杯赛:芯来RISC-V杯

RISC-V架构的显著性特征之一就是其开放的扩展性,它的扩展性体现在:

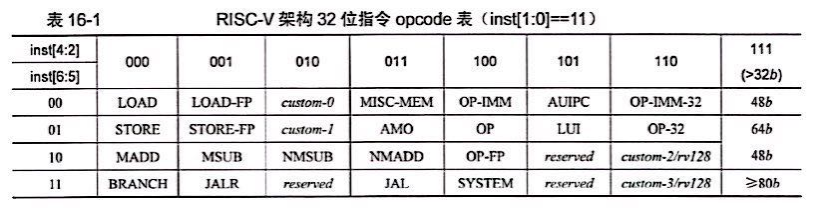

1)预留的指令编码空间

2)预定义的Custom指令

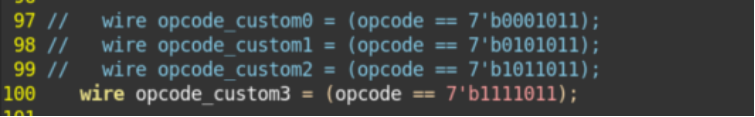

我们的设计中使用了32位长度指令,指令的低七位为opcode,各种不同的组合代表了不同的指令类型,我们用到了预定义的custom-3指令扩展协处理器指令,因此指令的opcode为7’b1111011。

由于蜂鸟E203处理器核基于Custom指令进行协处理器扩展,因此Custom指令也称为EAI指令。

EAI指令编码

32位的EAI指令编码格式如下:

1)opcode段:使用RISC-V架构中定义的Custom-1到4的指令组

2)xs1、xs2、xd:用于控制是否需要读源寄存器rs1、rs2和写目标寄存器rd

xs1:xs1=1,表示该指令需要读取rs1比特位索引的通用寄存器作为源操作数1;如果xs1=0,则表示不需要源操作数1

xs2:如果xs2=1,表示该指令需要读取rs2比特位索引的通用寄存器作为源操作数2;如果xs2=0,则表示不需要源操作数2

xd:如果xd=1,表示该指令需要写回结果到rd比特位指示的目标寄存器;如果xd=0,则表示不需要写回结果

3)funct7:可用作额外的编码空间,用于编码自定义指令(一种Custom指令组可以使用这一区间编码出128条指令)

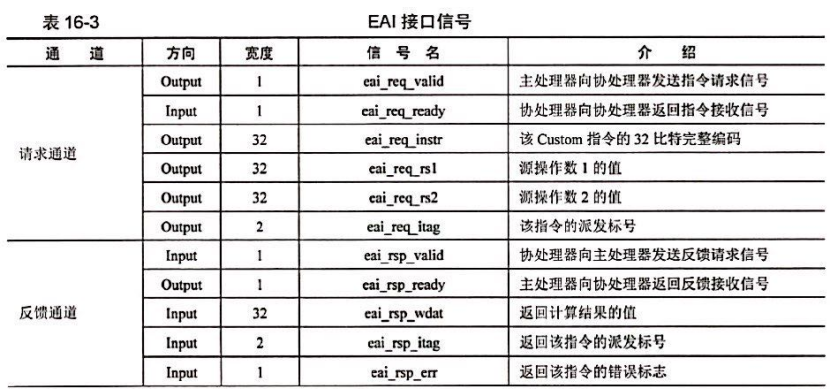

EAI接口信号

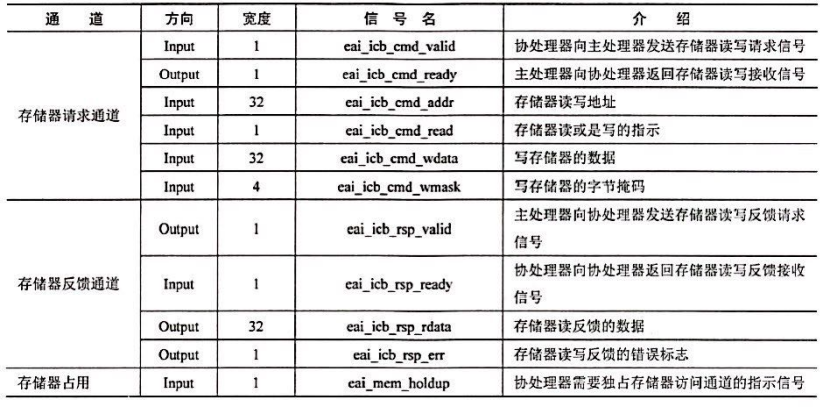

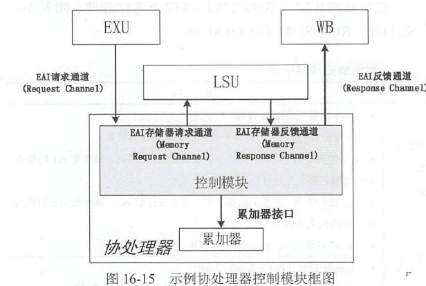

EAI接口主要包含4个通道:

l 请求通道(RequestChannel):主要用于主处理器在EXU级将指令信息和源操作数派发给协处理器。

l 反馈通道(ResponseChannel):主要用于协处理器反馈主处理器告知其已经完成了该指令,并将结果写回主处理器。

l 存储器请求通道(MemoryRequestChannel):。主要用于协处理器向主处理器发起存储器读写请求。

l 存储器反馈通道(MemoryResponseChannel):主要用于主处理器向协处理器返回存储器读写结果。