团队编号:CICC1156

团队名称:兔飞猛进

开发板:DDR200T

mig是Vivado中的DDR的控制IP核,他提供的AXI类型的总线接口可以实现DDR的访问

直接在IP Catalog中搜索mig即可

配置参数可参考此分享DDR200T中DDR的使用与时序介绍_全国大学生集成电路创新创业大赛_RISC-V论坛讨论_RISC-V MCU中文社区 (riscv-mcu.com)

成功配置完成mig后,可以打开其例子工程,新工程会自动生成ddr的模型,可以将相应的文件加入自己的工程中

注意在仿真时,需要在source中添加ddr3_model.sv和ddr3_model_parameters.vh文件,并实例化ddr模型,而在综合时不需要。

蜂鸟处理器核预留的内存拓展信号为icb总线协议,而mig的信号为axi总线协议,需要通过一个模块对这两种总线协议进行转换。

首先我们通过博客先了解一下这两种总线协议,

icb总线:【分享】关于ICB总线的应用_中国研究生创芯大赛_RISC-V论坛讨论_RISC-V MCU中文社区 (riscv-mcu.com)

axi总线:AXI总线介绍 - 迈克老狼2012 - 博客园 (cnblogs.com)

然后,对于两种总线协议的转换,蜂鸟在sirv_gnrl_icbs.v源文件中提供了sirv_gnrl_icb2axi模块,通过它可以优雅地进行协议转换

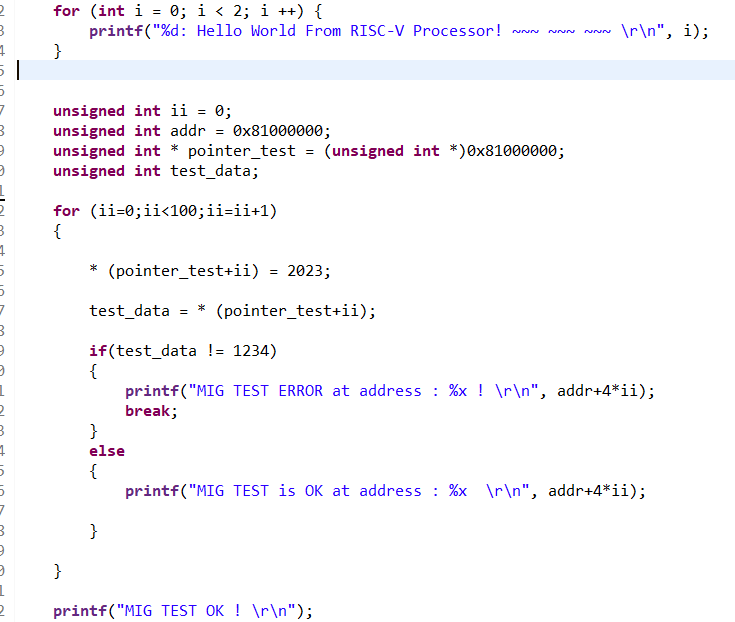

为了测试蜂鸟处理器对DDR的读写是否正确,编写了以下测试程序

值得注意的是,由于DDR与itcm和dtcm之间存在地址空间冲突,因此应该选择在一个不会发生冲突的地址进行测试,这里我们选择0x8100 0000,当然也可以通过设置itcmh和dtcm的基地址来解决冲突。

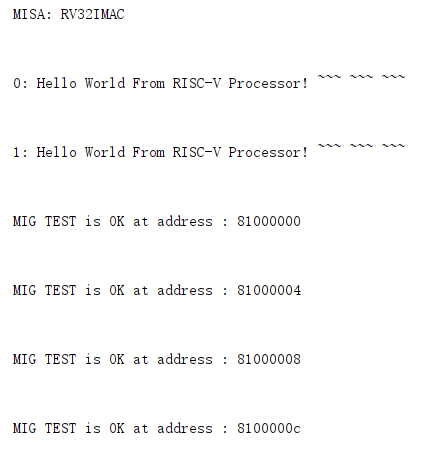

测试发现DDR读写正确,DDR内存拓展完成。