报名编号:CICC4035

团队名称:守序善良队

大家好,本篇是我们队伍的第五篇分享,主要内容是对于Radix-2除法器的简单介绍。水平有限,如有错误,欢迎大家批评指正。

E203中MDV模块的除法操作,采用普通的加减交替法,同样对于无符号乘法进行一位符号扩展后统一当作有符号数进行运算,因此需要33个迭代周期。另外,由于加减交替法迭代所得的结果存在着1比特精度的问题,因此还需要额外1个周期判断是否需要进行商和余数的矫正,和额外2个周期的商和余数矫正(如果需要矫正)最终得到完全准确的除法结果,总共最多需要36个周期。除法器进行运算周期较长,我们可以考虑使用不同的除法器算法来改良性能,此篇分享我们跟大家简单介绍一下Radix-2除法器。

Radix-2除法器是一种广泛应用于数字电路中的除法器,它的主要特点是利用二进制的性质来实现高效的除法运算,具有高速、灵活性较好、精度高、适用性广泛等优点。其工作原理基于二进制的长除法算法,通过将被除数和除数都表示成二进制数,并借助于诸如加法器、移位器等基本电路来实现逐位相除,从而得到商和余数。

在数字电路中,Radix-2除法器被广泛应用于各种需要进行高速除法运算的场合。例如,在计算机处理器、数字信号处理器、通信系统等领域都有广泛的应用。在这些应用中,Radix-2除法器通常作为关键的模块出现,以实现高效、快速的除法运算,从而提高整个系统的性能和效率。

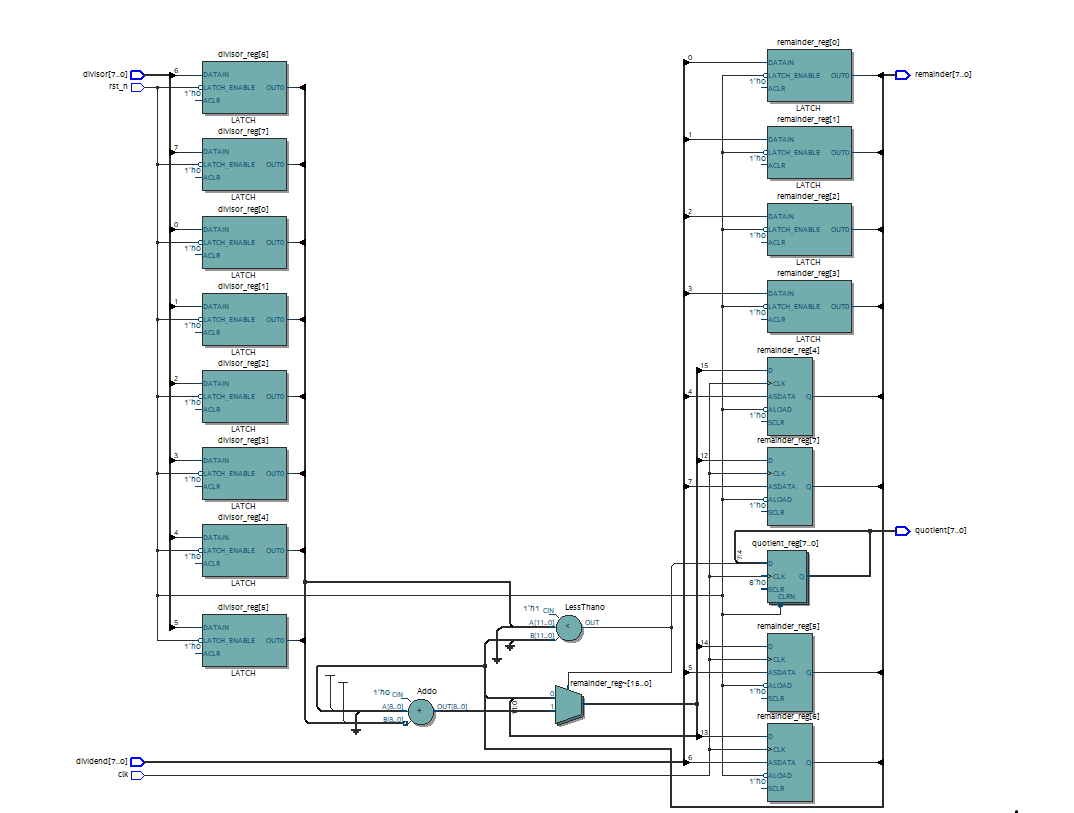

Quartus RTL图如下图所示

Quartus Post mapping图如下图所示

本文参考:

《手把手教你设计CPU》

https://blog.csdn.net/HFUT90S/article/details/129707444