DDR3读写控制器主要用于生成片外存储器DDR3 SDRAM进行读写操作所需要的时序,继而实现对片外存储器的读写访问。由摄像头采集得到的图像数据通常数据量较大,使用片内存储资源难以实现大量图像数据的缓存,因此借助开发板上存在的片外存储器DDR3 SDRAM对图像数据进行缓存。

DDR3 SDRAM(Double-Date-Rate Three Synchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,DDR3具有更高的运行性能与更低的电压。DDR SDRAM是在SDRAM技术的基础上发展改进而来的,同SDRAM相比,DDR SDRAM的最大特点是双边沿触发,即在时钟的上升沿和下降沿都能进行数据采集的发送,同样的工作时钟,DDR SDRAM的读写速度可以比传统的SDRAM快一倍。

DDR3读写控制器可以在Xilinx公司MIG(Memory Interface Generators)IP核的基础上设计得到的。IG IP核是Xilinx公司针对DDR存储器开发的IP,里面集成存储器控制模块,实现DDR读写操作的控制流程。下图所示是7系列的MIG IP核结构图。MIG IP核对外分出了两组接口,左侧是用户接口,右侧是DDR物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚。

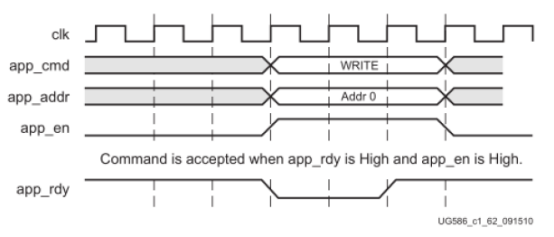

DDR3的读写都包含写命令操作,其中写命令(app_cmd)的值等于0,读操作app_cmd的值等于1。如下图所示写命令时序,在写命令的过程中,需要首先检查app_rdy信号的状态,当app_rdy为高电平时则表示此时的IP核命令接收处于准备好状态,可以接收用户命令,在当前时钟拉高app_en,同时发送命令(app_cmd)和地址(app_addr),此时命令和地址被写入。

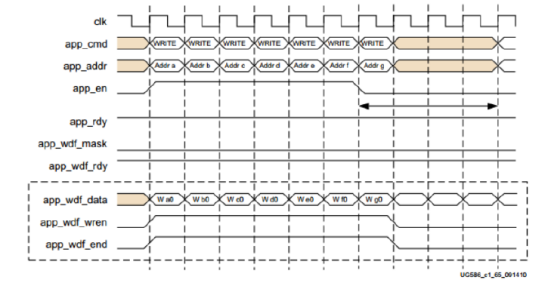

在DDR3的写数据过程中,在完成写命令之后需要进行写数据操作,如下图所示是背靠背模式下的写时序示意图,在写数据的过程中,首先需要检测app_wdf_rdy信号,该信号为高表明此时IP核数据接收处于准备完成状态,可以接收用户发送的数据,在当前始终拉高写使能(app_wdf_wren),给出写数据(app_wdf_data)。这样加上发起的写命令操作就可以成功向IP核写入数据。