队伍CICC2259 队员:刘宇轩 周嘉琪 冷思远

使用上述终端进入工程目录下hbird-sdk目录下的application/baremetal/benchmark/coremark文件夹,由于core_main.c文件原本在FPGA上执行,并没有定义CFG_SIMULATION,因此该程序执行的轮数iteration=500,这对于仿真而言数据量过大:

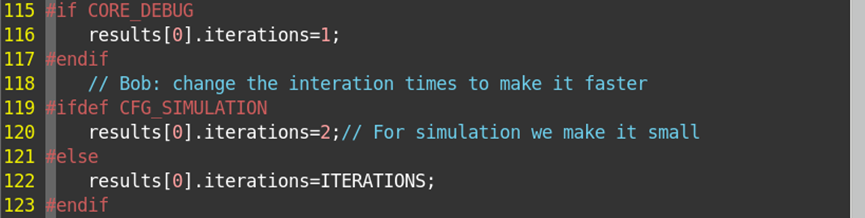

core_main.c中关于iterations的定义

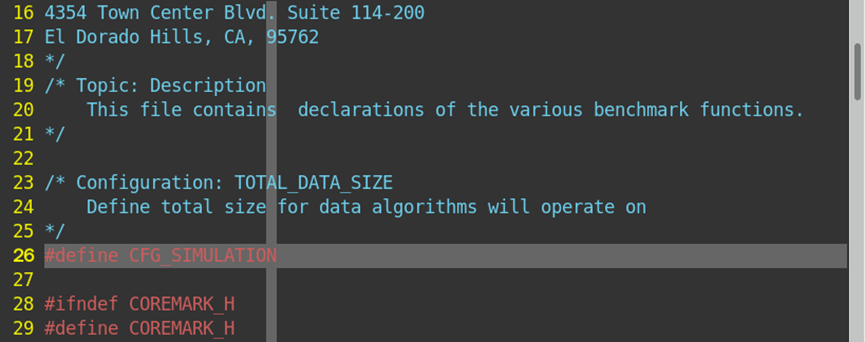

因此我们在头文件coremark.h中额外定义CFG_SIMULATION,使得该程序执行的轮数iteration=2来加快仿真速度:

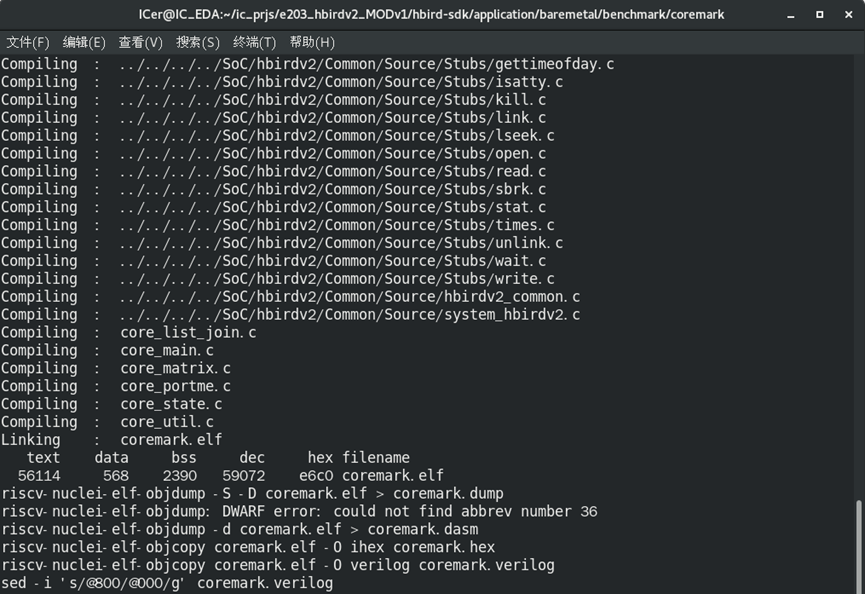

修改完c程序后,我们需要对其进行重新编译,在上述终端中执行make clean 然后执行make dasm SOC=hbirdv2 BOARD=mcu200t CORE=e203 DOWNLOAD=ilm PFLOAT=1。

如图所示为编译成功的info输出,告诉我们已经生成了coremark.verilog文件可用于仿真,以及coremark.elf文件可用于下载烧入。在仿真环境我们仅使用coremark.verilog文件。