本文利用NucleiStudio IDE 和 vivado 对 NICE demo协处理器进行软硬件联合仿真。

1. 下载demo_nice例程:https://github.com/Nuclei-Software/nuclei-board-labs/tree/master/e203_hbirdv2/common

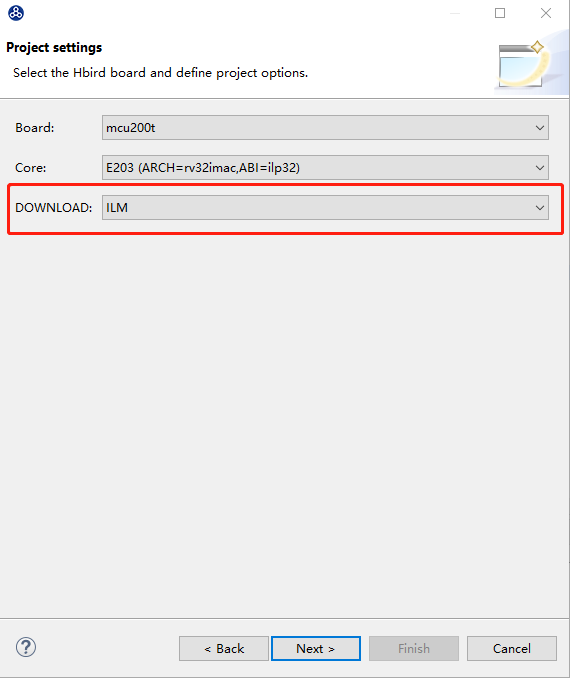

2.在NucleiStudio IDE 下新建一个c工程,并添加所需的源文件。注意在project settings的DOWNLOAD选项要选择ILM。

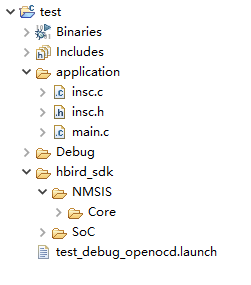

建好的工程如下图所示:

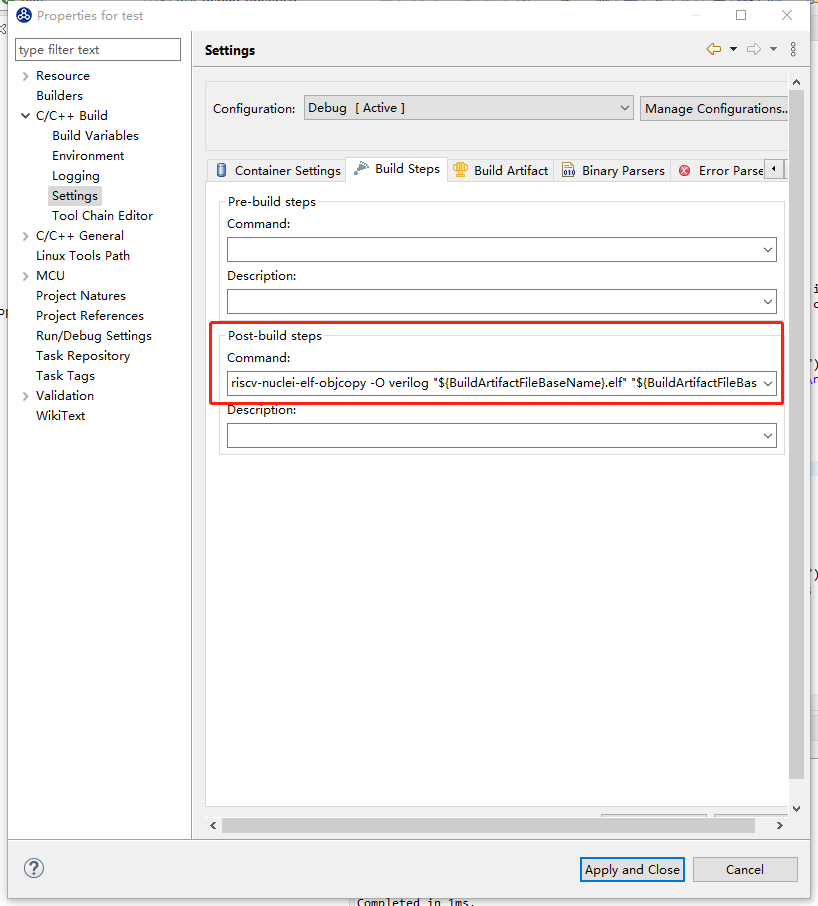

3.选择当前项目的properties->C/C++ Build->Settings->Build Steps->Post-build steps 增加如下命令:

riscv-nuclei-elf-objcopy -O verilog "${BuildArtifactFileBaseName}.elf" "${BuildArtifactFileBaseName}.verilog";sed -i 's/@800/@000/g' "${BuildArtifactFileBaseName}.verilog"; sed -i 's/@00002FB8/@00002000/g' "${BuildArtifactFileBaseName}.verilog";

使编译之后能生成.verilog文件。

4.编译工程,在Debug目录下找到tb需要的.verilog文件。

5. 下载蜂鸟E203硬件代码,里面包含了nice demo core的实现。下载地址:https://github.com/riscv-mcu/e203_hbirdv2

协处理器参考示例相关资料请参考:https://www.rvmcu.com/community-topic-id-340.html

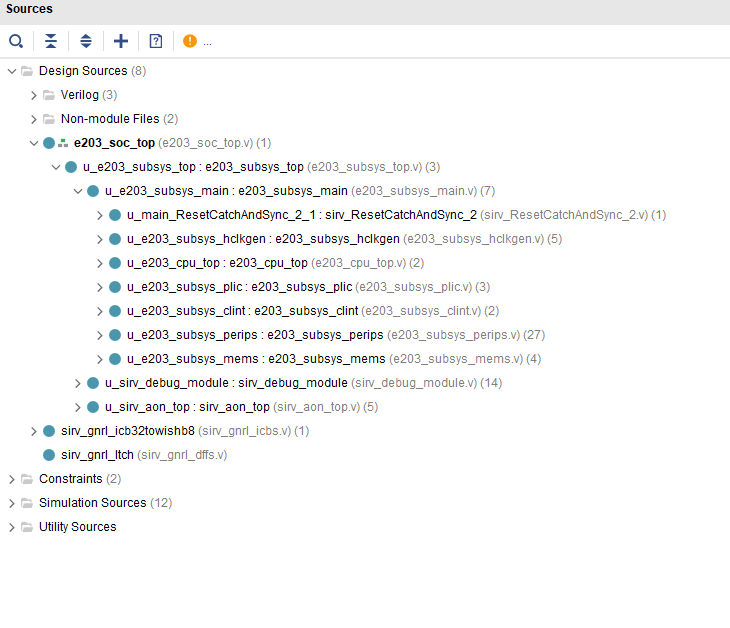

6.在vivado下新建一个工程,添加所有的rtl代码以及tb。

7.将e203_defines.v设置为global include ,并将文件类型改为 Verilog Header.

在config.v中增加宏定义: `define FPGA_SOURCE

8.将tb_top.v设置为顶层, 并添加读入.verilog文件的路径,保存文件。

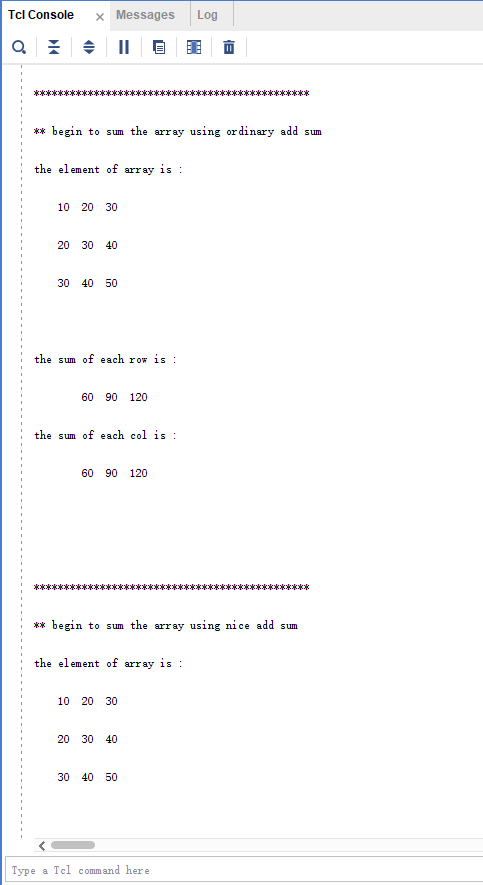

9.点击运行仿真。从 Tcl Console 上可以看到仿真运行正常,打印出了软件定义的相关信息。

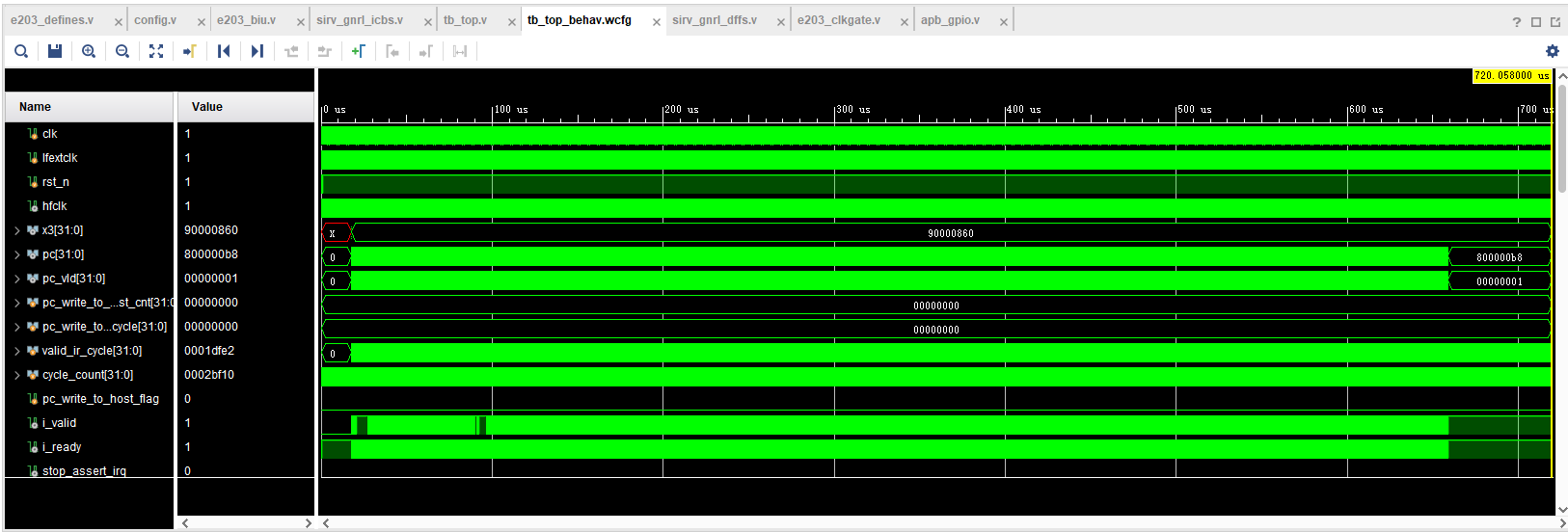

仿真波形:

至此,使用NucleiStudio IDE 和 vivado对蜂鸟E203+demo协处理器的软硬件协同仿真实验已经完成。根据以上步骤可以方便地对E203 SoC进行软硬件仿真调试。