队伍编号: CICC1842

由于FPGA内部存储资源有限,很多时候不能满足需求,因此可以利用DDR对系统进行存储扩展。由于DDR3内部控制十分复杂,因此可以基于AXI总线,利用Vivado提供的MIG IP对DDR3进行控制,使DDR3成为系统的一部分,可以直接通过地址进行读写。

在配置MIG时,主要注意以下几点:

1. Clock Period选择400MHz,Ratio选择4:1,则用户时钟(ui_clock: MIG IP给用户使用的时钟)就为400/(4:1)=100 MHz,即SoC中MIG IP核通过AXI总线连接100 MHz时钟。

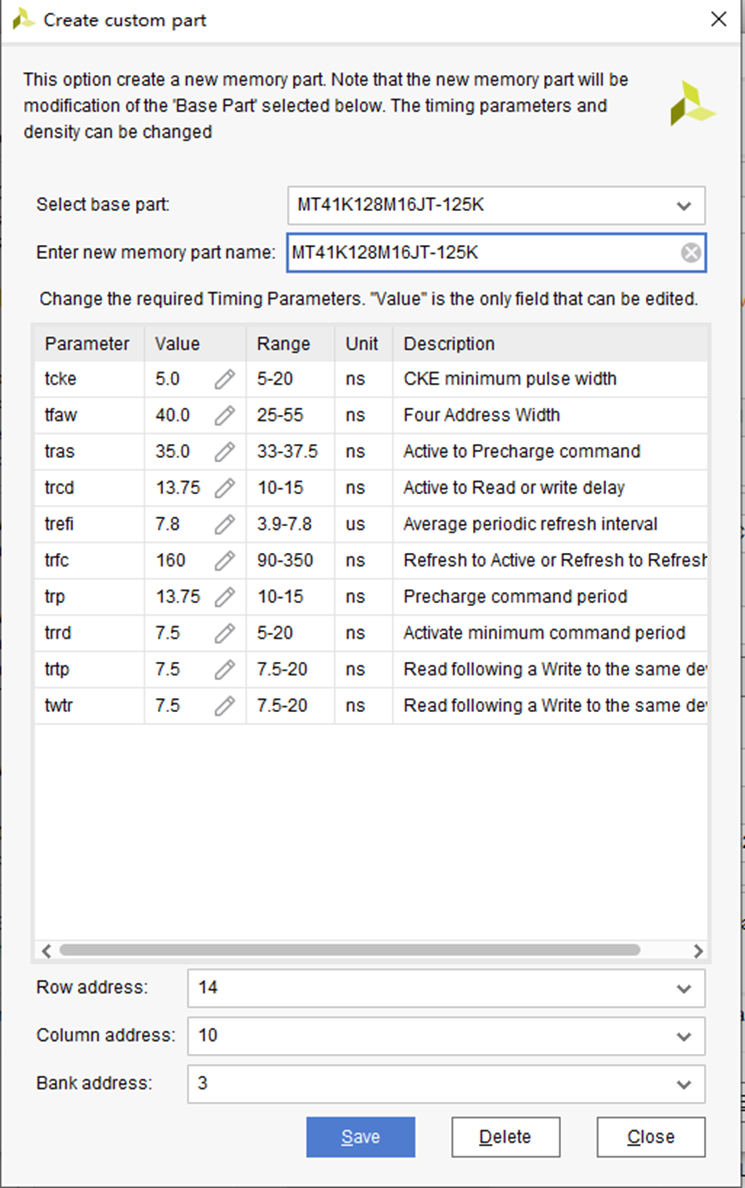

2. Memory Part需要自己建立,因为没有和开发板完全对应的DDR3型号。注意:此处不可随便选,DDR3型号不对应无法工作!Nuclei DDR200T FPGA开发板使用的是MT41K128M16JT-125K,配置如下:

3. Input Clock Period选择200MHz, 此时钟是给DDR3运行时钟,

4.UCF文件需要根据原理图自行配置。

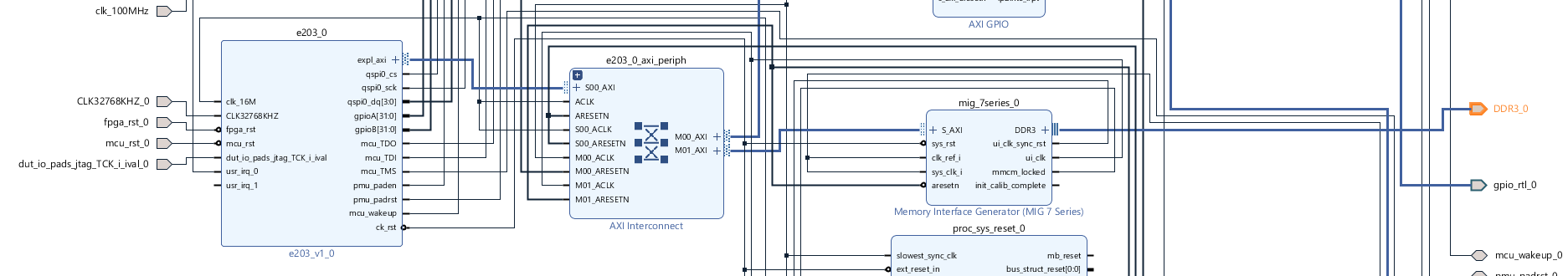

配置完成MIG后,由于e203与MIG(100MHz)时钟频率并不一致,可以将e203降频至10MHz,并通过AXI-Inerconnect进行跨时钟处理,具体连接如下

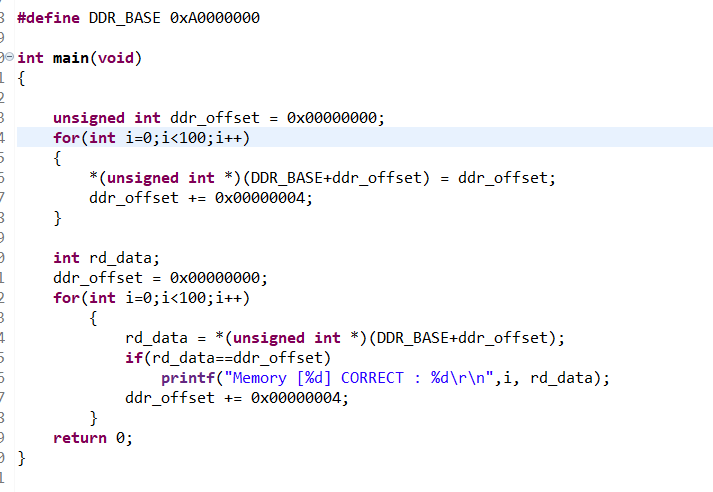

其中ui_clk连接到M01_ACLK端口,clk_16M连接到S00_ACLK。测试程序如下,

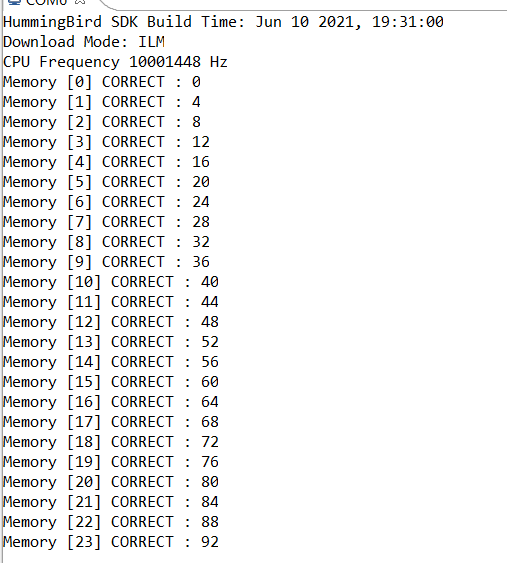

本程序向MIG写入100个数据,再将其读出,如果写入与读出一致,则打印正确标识。经过测试,DDR3工作正常。