喜欢0次

团队名称:Cambrain_20

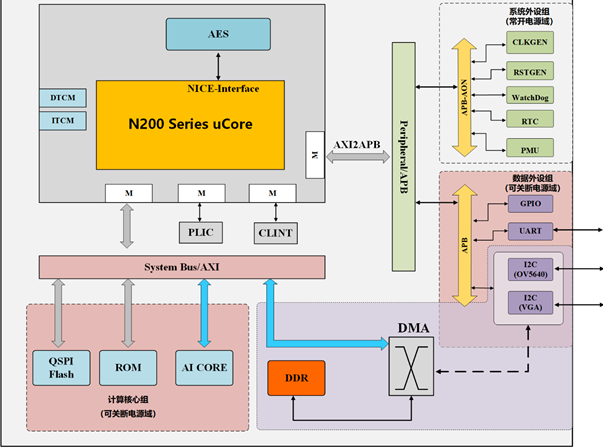

这个是我们整体的架构图。我们SOC主要包括了三个模块组,计算核心组,系统外设组,数据外设组。计算核心组包括了RISCV内核,RISCV内核中集成了一个ITCM和DTCM的指令存储器和数据存储器。另外留有两个中断接口:PLIC和CLINT中断接口和AXI系统总线接口。RISCV内核还留有协处理器接口NICE,NICE接口可扩展RiscV指令集,因此我们将AES加密核挂接到此处。

接下来是总线介绍,我们的总线划分为系统总线和外围设备总线。其中系统存储总线使用AXI高速总线IP。AXI总线上挂载了 Ai core ROM和flash还有DMA。外围设备总线APB通过AXI to APB桥接器与AXI总线进行连接。APB总线外设分为两个部分,一个常开电源域。此处APB挂接的是与时钟,电源,复位,中断相关的系统外设。另外一个是数据外设域APB挂接了SPI I2C GPIO UART 等设备。