一、团队介绍

大家好,我们是293小分队,报名编号为CICC1363。本次我们将分享VDMA IP核的基础知识。水平有限,如果有错误希望大家多多批评指正。

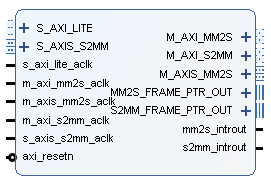

二、VDMA端口信号

S_AXI_LITE:PS端可以通过AXI_LITE协议对IP核进行控制;

S_AXIS_S2MM:视频流(AXI STREAM)输入到IP核的FIFO中;

S_AXIS_MM2S:IP核的FIFO生成视频流(AXI STREAM)输出到后端;

S_AXI_S2MM:IP核的FIFO中的像素数据存入memory;

S_AXI_MM2S:memory中的像素数据输出到IP核的FIFO中;

s_axi_lite_aclk、s_axi_mm2s_aclk、s_axis_mm2s_aclk、s_axi_s2mm_aclk、s_axis_s2mm_aclk分别为上述端口的控制时钟,一般采用同一频率时钟。

mm2s_introut和s2mm_introut分别为MM2S和S2MM通道完成后的中断信号输出。

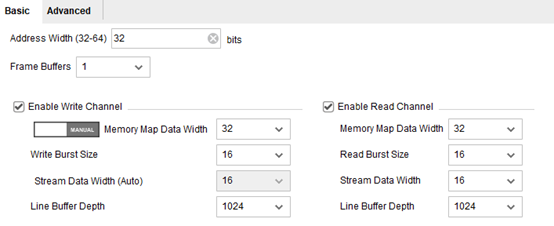

三、VDMA基础设置

Address Width:地址宽度,与memory一致;

Frame Buffers:帧缓存数量,当选择1时,则输入输出皆在同一块内存中;当选择2及以上时,则输入输出操作不同内存区域,且交替进行;

Memory Map Data Width:S_AXI_S2MM或S_AXI_MM2S通道的数据位宽,且必须大于视频流数据位宽;

Burst Szie:AXI猝发传输大小,一般设置为16;

Stream Data Width:视频流数据位宽,一般由VDMA前端输入自动确定;

Line Buffer Depth:S_AXIS_S2MM或S_AXIS_MM2S通道FIFO,当输入输出视频帧率相当时,可以适当选择较小深度,当输入输出视频帧率差别较大时,需要加大FIFO深度。

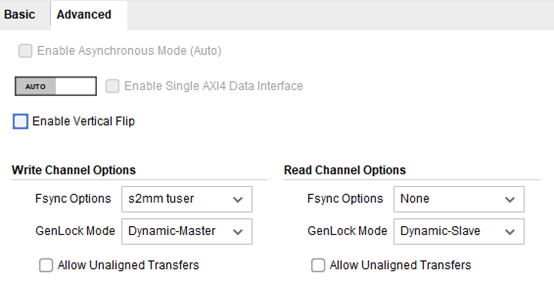

对于写通道,同步选项选择s2mm tuser,即当一帧视频的第一个像素到来时,s2mm tuser被拉高,VDMA开始写入memory;

对于读通道,同步选项选择None,即只要后端准备好接受数据,ready信号为1时,VDMA即开始输出像素点;

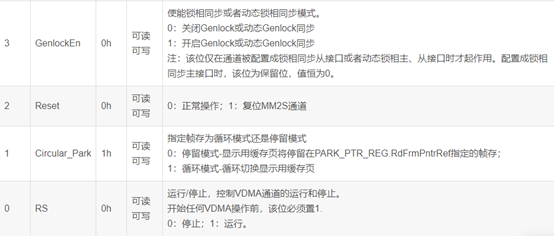

至于GenLock Mode,写通道和读通道分别选择Dynamic-Master和Dynamic-Slave,即写通道依次写入0,1,2···,而读通道每次读取写通道上一帧数据,并且写通道和读通道都可以跳过对方正在操作的帧。

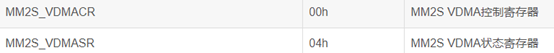

四、VDMA寄存器设置

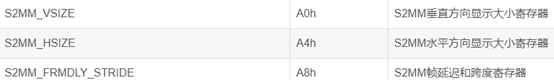

主要有以下几个重要寄存器:

注意:HSIZE和STRIDE都是以Byte为单位,且VSIZE设置必须放置在所有寄存器设置的最后。