一、团队介绍

大家好,我们是做大做强队,报名编号是CICC1025。本次我们分享音频信号处理系统的协处理器的乘累加过程。水平有限,如有错误,希望大家批评指正。

二、协处理器简介

RISC-V具有很高的可扩展性,既预留出了指令编码空间,也提供了预定义的Custom指令;RISC-V的标准指令集仅使用了少部分指令编码空间,更多的指令编码空间被预留给用户进行扩展指令蜂鸟E203借鉴了开源RISC-V处理器Rocket Core的协处理器接口RoCC,为了与原始接口进行区分,命名为EAI(Extension Accelerator Interface)接口。

三、硬件加速简介

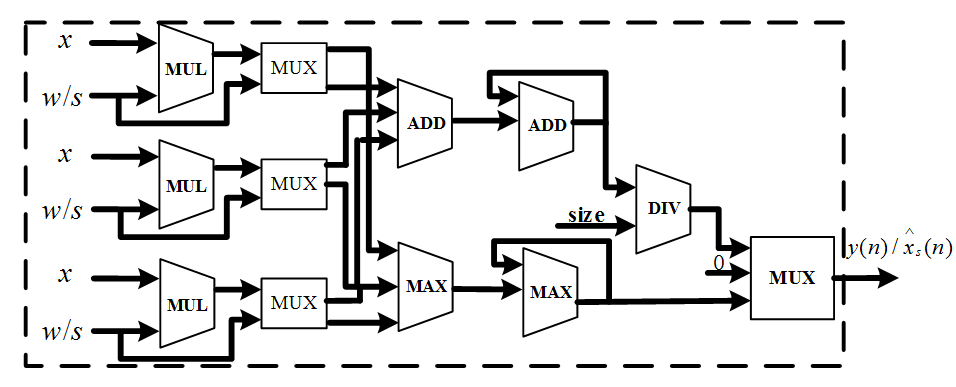

图1 乘积累加运算单元

乘积累加运算单元电路,类似于DSP中的MAC指令,能够快速的实现 C=B+AB格式的运算功能

图2 卷积运算单元

卷积运算电路,采用3个乘法器进行卷积加速,对一行数据进行操纵,后接累加器进行卷积结果累加得到运算结果。

利用乘积累加运算特性,规定相关协处理器的自定义指令。然后对指令进行乘积累加运算电路模块化。从而快速的实现乘积累加的功能,并将此功能运用到FxLMS算法中权值更新的部分,从而让这一部分的运算速度得到提升。

测试结果

通过两行向量,对其进行卷积运算,可以得到如上图所示结果,通过多组测试,结果均正确,因此可以得出卷积运算部分功能实现。

上图是卷积运算和采用协处理器实现方式,得出的指令数和周期数对比情况。可以得知卷积运算加速器有比较好的加速能力。