大家好,我们是这是一件好事队,队伍编号为CICC1859,该文章分享的是基于蜂鸟E203内核的SoC设计中,主机通过NICE总写队协处理器内存及寄存器的读写控制思路。

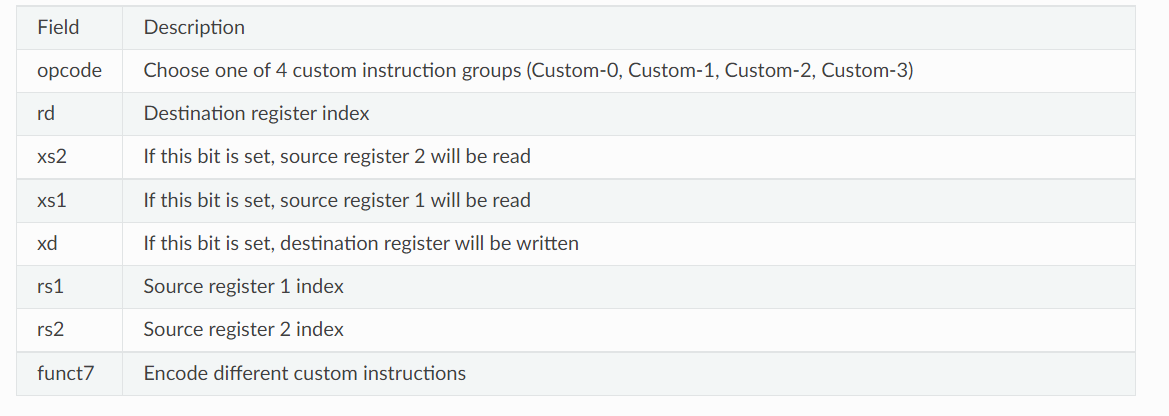

在我们的作品中通过指令的funct7段定义了如下两条自定义汇编指令:

skram从协处理器RAM发送数据到蜂鸟E203内核RAM

lkreg 从蜂鸟E203内核RAM发送数据到协处理器寄存器

skreg 从协处理器寄存器 发送数据到 从蜂鸟E203内核RAM

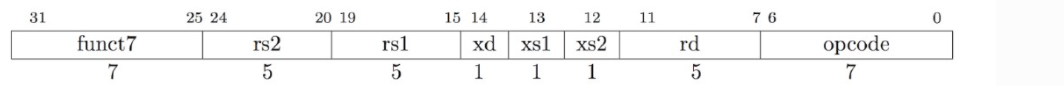

指令格式:

设计思路:将源地址、目标地址、数据长度通过rs1和rs2寄存器传输。模块内有一个带有使能和直接置数的自增地址计数器负责控制ICB总线和KRAM或者寄存器的读地址。协处理器中还有一个地址缓存寄存器,用来暂存写入地址,等待数据到来后再刷新,即当ICB总线繁忙时,计数器和缓存寄存器暂停刷新,直到总线回应才会继续计数。从总线到KRAM时,计数器存储总线地址,缓存寄存器存储KRAM地址;从KRAM到总线时,计数器存储KRAM地址,缓存寄存器存储总线地址,这样保证了数据能被准确无误地传输。

具体定义如下:

协处理器RAM操作指令

| 寄存器及其对应位宽 | 代表含义 |

| rs1[31:0] | ICB总线起始地址 |

| rs2[15:0] | 协处理器RAM起始地址 |

| rs2[31:16] | 读写的数据长度 |

协处理器寄存器操作指令

| 寄存器及其对应位宽 | 代表含义 |

| rs1[31:0] | ICB总线起始地址 |

| rs2[31:0] | 协处理器RAM起始地址 |