大概花了三天时间完成了蜂鸟E203 SOC在zynq7100 FPGA的移植工作,并完成了hello world程序的在线debug调试。

蜂鸟E203的移植在网上有大把的demo,其中bit文件固化存在的问题并不大,只需要按照硬件电路完成管脚的删减和映射(约束)即可,这里重点说明一下debug出错问题的解决思路。

我在FPGA固化文件完成后,在上位机SDK中debug helloworld demo时发现hello_world.elf文件无法下载成功。

因为自己用的是芯来专用的JTAG debugger,但是没有用芯来专用的FPGA开发板,因此是使用跳线连接JTAG。因此我首先怀疑是跳线解错了导致,经过JTAG线序对应关系检查、将DI和DO交叉测试,debug ERROR信息均相同,因此排除JTAG线序错误原因。

然后我怀疑是蜂鸟E203复位电平存在问题导致,因此将复位按钮持续按下去进行调试,然后将复位按钮正常状态进行调试,debug ERROR信息军相同,因此排除是复位电平导致错误。

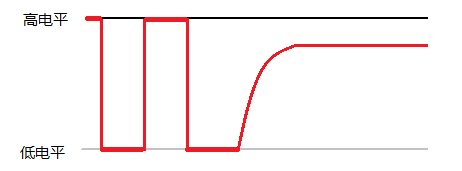

然后我怀疑是蜂鸟E203时钟无信号导致,因此通过示波器观察JTAG DO信号,通过示波器观察JTAG SCK和DI\DO信号,发现SCK和DI信号正常,符合JTAG时序,同时DO信号有高低电平变化,说明蜂鸟E203时钟是有信号的,同时JTAG逻辑工作正常,但是观察DO信号在无信号输出时,其波形是一个缓慢上升的波形,同时上升趋势结束后,其电平和高电平低一些,如下图1所示:

图 1 JTAG DO波形图

然后和DI输出波形图对比之后,感觉这里不太对,经过思考,system.v中对一JTAG 管脚属性都是inout,在模块里面用了IOBUF原语做了IO管脚的IO方向适配,因此,当DO的输出有效时,其高低电平由E203的JTAG模块确定,而当DO输出无效时,该管脚被IOBUF定义为高阻,上图1中波形出现缓慢上升的时间就是DO为高阻的时间。

因此我在system中将JTAG的DO管脚定义为output,同时将对应的IOBUF原语取消掉,再次进行debug调试,功能就符合预期了。