对话芯来科技胡振波:车规、AI与RISC-V IP 2.0模式

RISC-V因其开放标准的特性受到广泛关注。在RISC-V车载应用领域,国外有英飞凌、NXP、瑞萨、博世和ST等传统汽车芯片巨头共同成立合资企业重注RISC-V车用芯片,国内有东风汽车正式发布了基于RISC-V架构的车规级芯片产品。东风汽车代号为DF30,功能安全等级达到ASIL-D,其内核IP便来自于芯来科技NA900系列。在ICCAD-Expo 2024期间,NE时代有幸与芯来科技创始人胡振波展开交流,共同探讨RISC-V未来在车载领域的进展和未来的发展趋势。芯来科技已经推出多个符合车规要求的RISC-V内核IP。芯来科技NA系列CPU IP(NA900和NA300)已获得了功能安全等级ASIL D的认证证书,NA900也就是东风汽车DF30车规级MCU所用的内核IP。芯来科技成立于2018年,一直专注于RISC-V CPU IP及相应平台方案的研发,目前已经推出了N、U、NX、UX四大通用CPU IP产品线和NS、NA、NI三个专用CPU IP产品线。“RISC-V在车载领域的落地其实非常快,目前芯来科技合作的车载客户已超过数十家”,胡振波开门见山的说道。01.

胡振波认为,RISC-V在车载领域反而很有希望落地。其中最关键的因素在于相比于其他行业,车载领域的门槛虽然较高,但其要求却相对封闭,整个需求体系比较明确,在底层硬件规范好,反而对软件生态的依赖较轻。

RISC-V开放标准的特点,灵活性相对更高。并且,RISC-V整个行业均处于初期发展阶段,国内已经在新能源、智能化方面证明了对新技术应用的引领性。因此,RISC-V也更容易在国内市场上得到快速推广。但需要正视的是,RISC-V发展很快,留给国内的发展窗口期可能仅有2-3年。在这个过程中,需要全行业生态各个环节企业共同的努力。从应用来看,由于当前RISC-V应用生态的薄弱,胡振波认为在智能座舱等需要Android应用的领域RISC-V尚有距离。而在其他领域,包括不限于各类控制从车窗座椅、底盘动力到自动驾驶应用前景巨大。02.

芯来科技在今年6月六周年之际推出了RISC-V IP 2.0的服务模式,由之前IP授权的商业模式转变为IP订阅的商业模式。将CPU IP从传统的“按项目授权”模式,提升到“订阅式”模式,助力本土设计公司更高效的完成CPU

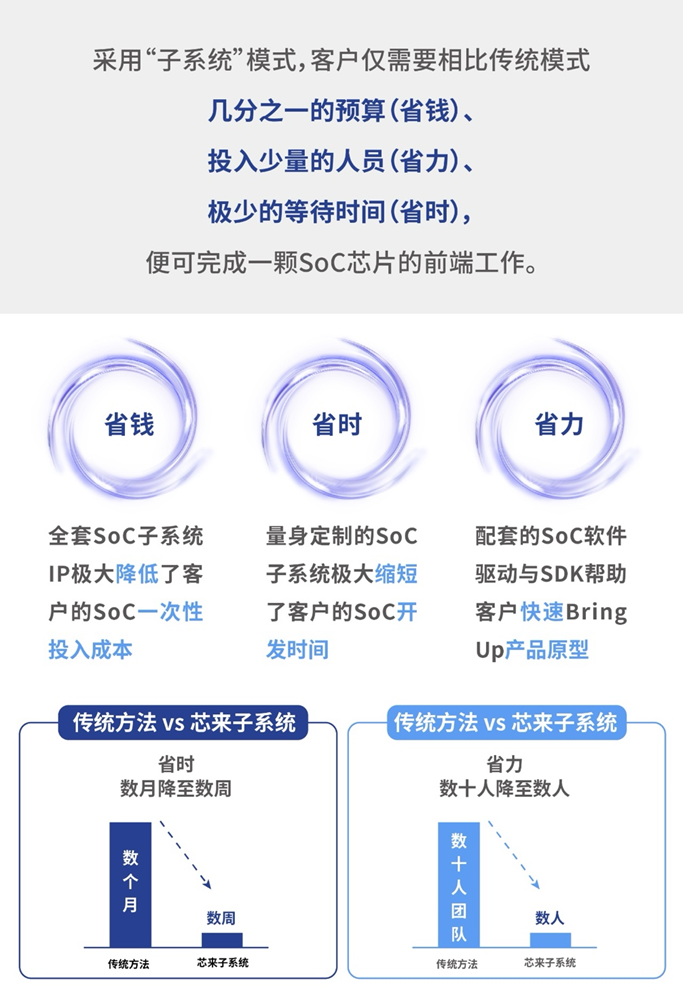

IP的采纳与授权过程,大幅缩减CPU IP的授权成本和时间成本,集中精力去做具体场景的SoC芯片产品。因此芯来科技从客户的需求出发推出了订阅制的服务模式,即RISC-V CPU IP “随芯包”模式。一次订阅后,订阅期内可以无限使用。在订阅期内客户可以按需订阅,随时升级。并且也能享有最新的IP特性。目前芯来科技已经将N100、N200、N300、N600、N900;U600、U900 (支持MMU);NX600、NX900;UX600、UX900 (支持 MMU)纳入“随芯包”订阅模式的范畴。“随芯包”可以帮助客户一次性订阅无限次使用、按需订阅随时升级以及实时享有最新IP特性。不仅如此,芯来科技的IP 2.0战略除“随芯包”模式还提供了“子系统”的服务。具体合作流程为,当客户提出需求时,芯来科技可以按照客户需求搭建一个包含CPU IP、总线和基础外设的平台,为客户达到省钱省时省力的目的。胡振波透露,从需求提出到系统搭建,芯来科技可以以周为单位的时间完成交付和迭代,其中包括CPU IP,总线,外设,底层驱动等等。大幅降低客户工程开发时的工作量。03.

胡振波首先介绍了AI芯片的组成,主要包括三部分,分别是CPU IP作为芯片内部的管理(House Keeping),NPU IP作为AI加速器,以及用于处理并行计算的VPU IP。在CPU IP中,之前以ARM授权IP为主,现在RISC-V提供了额外的一个选项,可以作为CPU IP来使用,作为对ARM的一个替代。对于NPU而言,在AI芯片中,都强调可编程的能力,以应对AI迭代的速度。在这种情况下,单纯的纯硬件NPU很难满足需求,现在有的NPU内部的每个计算节点,都可能使用一个CPU Core作为基础的计算节点元素,对于这种运算节点的CPU Core,ARM很难进行修改和扩展,而RISC-V的Core可以很好地充当基础的“计算节点”元素来满足NPU可编程的要求。最后,对于并行计算的VPU IP,胡振波解释道,这是因为AI对灵活算子的要求越来越高,纯硬件化NPU无法全部满足。以往矩阵运算可能占到80-90%,但现在随着大模型的应用,对灵活算子的要求越来越高,需要具有一定并行算力(譬如Vector宽度达到512甚至1024Bits)且软件灵活的VPU IP并行计算VPU IP和NPU并不矛盾,两者都是AI芯片的重要组成部分。虽然ARM也有并行计算的SVE指令集,但SVE的ARM CPU IP更多的是面向服务器领域。基于RISC-V Vector指令集的RISC-V VPU IP能够很好的满足这一诉求。目前国内有代表性的此类IP主要是芯来科技的NI900系列RISC-V IP。04.

针对RISC-V的生态问题,胡振波强调相比于ARM生态,RISC-V是一个开放标准,开放的生态。芯来科技只是其中重要的一份子,并不是全部。全世界全产业都会共同推动,众人拾柴火焰高,RISC-V的生态会越来越好,参与者都会跟着水涨船高。可以看出RISC-V已经在车载领域得到加速应用,这其中离不开技术的进步,更离不开商业上的持续坚持。芯来科技长期深耕RISC-V CPU IP,将持续与生态伙伴共同推动RISC-V向前发展。备注:ICCAD-Expo 2024(上海集成电路2024年度产业发展论坛暨第三十届集成电路设计业展览会)由上海市经济和信息化委员会、浦东新区人民政府、中国半导体行业协会集成电路设计分会指导,上海市浦东新区投资促进中心支持,上海张江高科技园区开发股份有限公司和上海芯媒会务服务有限公司共同主办,本次大会以“智慧上海,芯动世界”为主题。期间,NE时代作为受邀合作伙伴与包括西门子EDA、TSMC、芯易荟、锐成芯微、芯启源、奎芯科技、巨霖科技、速石信息、合见工软、荣芯半导体、摩尔精英、芯原微电子、思尔芯、国微芯、芯行纪、鸿芯微纳、芯来科技、芯华章、芯耀辉、英诺达、芯和半导体在内的多家芯片半导体企业创始人及核心骨干深入探讨芯片及EDA、IP发展的趋势与未来,车规芯片发展的挑战与进展等核心话题。

*免责声明:以上内容仅供交和流学习之用。如有任何疑问或异议,请留言与我们联系。