近日,西门子EDA与芯来科技宣布达成战略合作:西门子EDA的Tessent™ Enhanced Trace Encoder增强型追踪编码器解决方案已全面支持芯来RISC-V处理器内核,该解决方案将为选择芯来科技RISC-V CPU IP的客户提供一种实时监控CPU程序执行的机制。它将在SoC层面对程序执行(指令跟踪)以及可选的加载和存储指令中的数据(数据跟踪)进行编码,以高度压缩的格式输出跟踪,使用户在复杂的异构设计中显著提高生产效率。

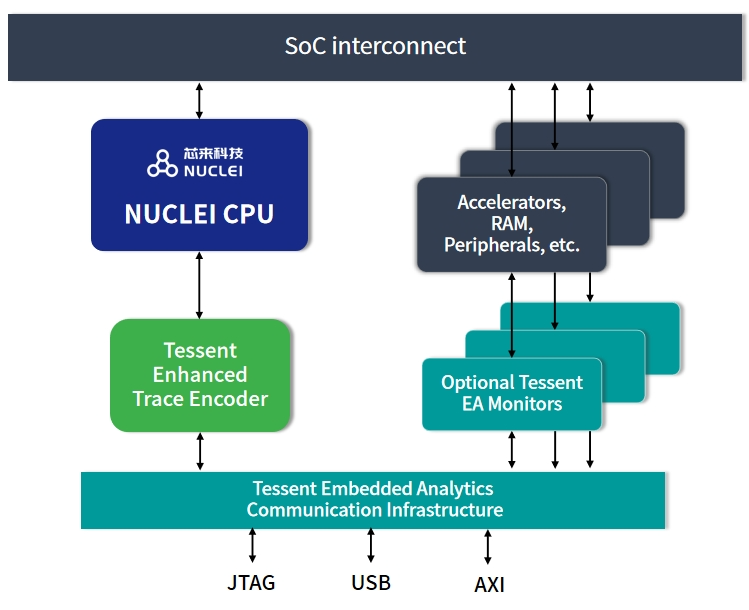

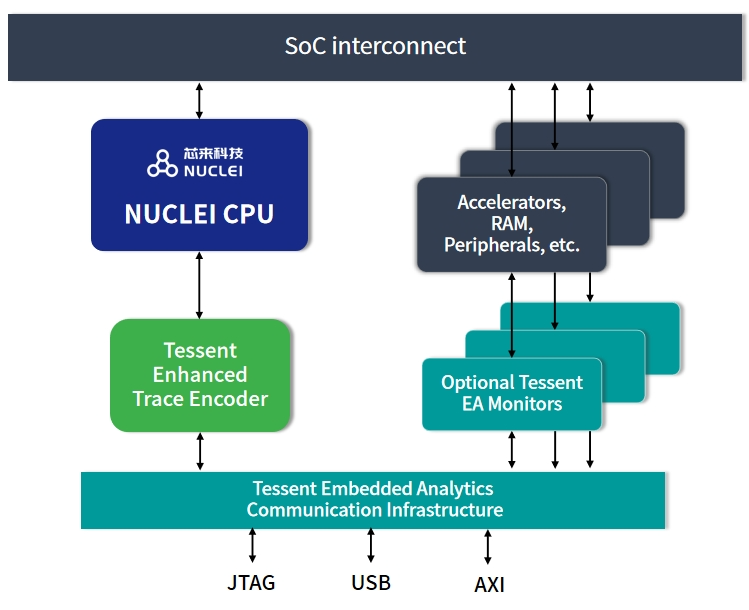

Nuclei System Technology today announces a strategic collaboration with Siemens Digital Industries Software. The companies are working on full Tessent™ Enhanced Trace Encoder solution support for Nuclei's RISC-V processor cores. The collaboration provides real-time monitoring of CPU program execution for customers choosing Nuclei System Technology's RISC-V CPU IPs. It encodes program execution(instruction tracing) and optional loading and storing of data in highly compressed formats at the SoC level, significantly enhancing production efficiency for users in complex heterogeneous designs.Tessent Enhanced Trace Encoder增强型追踪编码器解决方案是西门子EDA的Tessent Embedded Analytics嵌入式分析产品线成员产品。通过这一联合解决方案,开发人员可以有效地追踪和调试芯片和软件之间的问题,并能准确了解基于芯来RISC-V CPU IP的实时运行状态。Tessent Enhanced Trace Encoder增强型追踪编码器完全满足RISC-V基金会调试和追踪工作组(Debug and Trace Working Group)制定的标准规范,同时还支持自定义指令的调试跟踪,为用户提供了一个更为高效的调试工具环境,在复杂系统的开发中能够显著提升的研发效率。

Siemens' Tessent Enhanced Trace Encoder solution is part of Siemens' Tessent Embedded Analytics product line. Through this combined solution, developers can effectively trace and debug issues between chips and software, gaining accurate insights into real-time operational states based on Nuclei's RISC-V CPU IPs. The Tessent Enhanced Trace Encoder solution fully complies with the Efficient Trace(E-Trace) standard specifications set by the RISC-V Foundation Debug and Trace Working Group. It also supports debugging traces for custom instructions, providing users with a more efficient debugging tool environment that significantly enhances research and development efficiency in complex system development.

芯来科技拥有丰富的RISC-V CPU IP矩阵,覆盖从低功耗到高性能的各种应用需求,遍及5G通信、工业控制、人工智能、汽车电子、物联网、存储、MCU、网络安全等多个领域。芯来科技的RISC-V CPU IP具有高度可配置性,用户可以在上百个选项中根据实际需求选择最贴近下游应用的配置,并实现最大程度的优化。此次合作整合了RISC-V处理器IP集成和调试追踪工具,更进一步提高了客户芯片研发的效率。

Nuclei System Technology provides a rich portfolio of RISC-V CPU IPs covering various applications from low power to high performance in areas such as 5G communication, industrial control, artificial intelligence, automotive electronics, IoT, storage, MCU, network security, etc. Nuclei's RISC-V CPU IPs are highly configurable, allowing customers to optimize configurations based on actual downstream application needs from hundreds of options. This collaboration combines RISC-V processor IP integration and debugging trace tools, further improving the efficiency of customer's chip development process.芯来科技CEO彭剑英表示:芯来科技的RISC-V CPU IP具有业界最高的质量控制标准。为了提升用户的使用体验和优化客户SoC设计中的调试方案,我们需要一个像Tessent Enhanced Trace Encoder增强型追踪编码器这样的优质工具协助我们的下游客户进行开发工作,该工具的引入将能为我们的客户提供更为高效的调试和跟踪方案。”

CEO of Nuclei System Technology, Dr. Jianying Peng, said:"Nuclei System Technology's RISC-V CPU IPs adhere to the highest industry quality control standards. To enhance user experience and optimize debugging solutions in our customers' SoC designs, we need high-quality tools like the Tessent Enhanced Trace Encoder to assist our downstream customers in their development process. The availability of this tool will provide our customers with more efficient debugging and tracing solutions."“Tessent Embedded Analytics嵌入式分析工具可实现全系统实时调试和部署后的分析,从而帮助使用者产出高质量的、创新的产品,并将其快速推向市场。”西门子EDA Tessent部门副总裁兼总经理Ankur Gupta说道,“芯来科技作为中国大陆领先的RISC-V解决方案提供商,服务了大量的芯片客户,我们很高兴能够与其成为合作伙伴关系共同支持目标客户的芯片研发。” Ankur Gupta, VP and General Manager, Tessent, Siemens Digital Industries Software, said: "Siemens' Tessent Embedded Analytics tools enable real-time debugging and post-deployment analysis of the entire system, helping users produce high-quality, innovative products and rapidly bring them to market. As a leading RISC-V solution provider, Nuclei System Technology serves a large number of chip customers, and we are pleased to partner with them to jointly support the chip development goals of our mutual customers."芯来科技与西门子EDA此次合作的达成,将极大的提升RISC-V CPU IP的客户的研发效率,对RISC-V生态建设起到积极的推进作用。The collaboration between Nuclei System Technology and Siemens is expected to greatly enhance the research and development efficiency of RISC-V CPU IPs' customers, positively contributing to the advancement of the RISC-V ecosystem.

芯来科技成立于2018年,一直专注于RISC-V CPU IP及相应平台方案的研发,是本土RISC-V领域的代表性企业。芯来科技从零开始,坚持自研,打造了N/U、NX/UX四大通用CPU IP产品线和NS、NA、NI三个专用CPU IP产品线。其中:

* N/U(支持SV32 MMU)是32位架构,主要用于边缘计算、低功耗和IoT场景;* NX/UX(支持SV39和SV48 MMU)是64位架构,主要用于数据中心、网络安全、存储等高性能应用场景;* NS(Security)面向支付等高安全场景;* NA(Automotive)面向功能安全汽车电子场景;* NI(Intelligence)面向AI等高性能计算场景。目前已有超过200家国内外正式授权客户使用了芯来科技的RISC-V CPU IP,遍及AI、汽车电子、5G通信、网络安全、存储、工业控制、MCU、IoT等多个领域。▼往期精彩回顾▼

NucleiStudio 2022.08更新版本发布