本土RISC-V CPU IP领军企业——芯来科技正式发布基于RISC-V处理器的HSM子系统解决方案,提供专业有效的信息安全保护以及加解密功能。

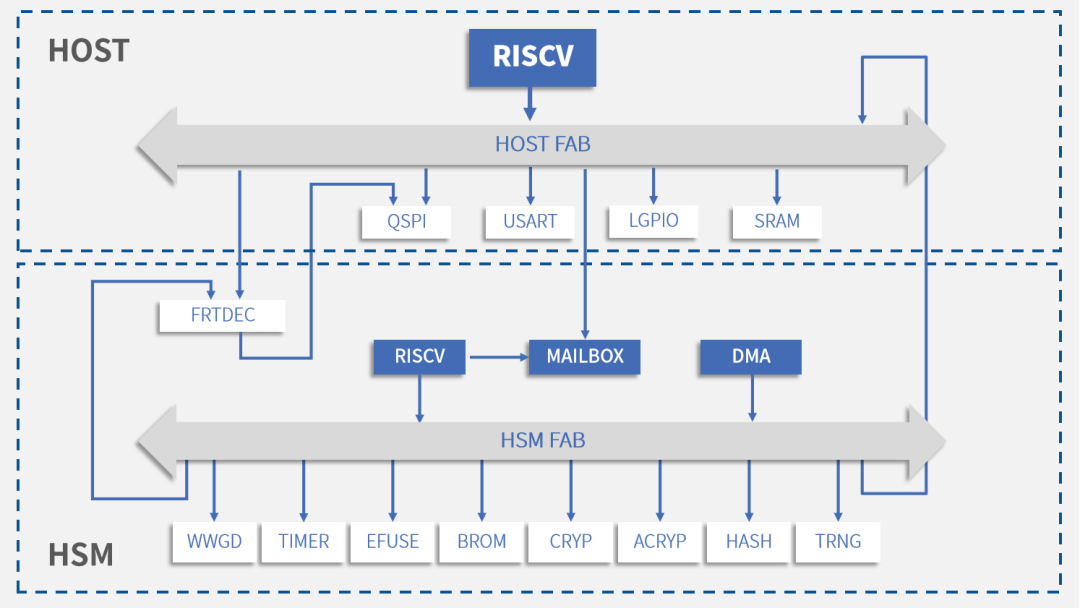

芯来科技提供与Host系统紧耦合的HSM子系统,主要包含控制、通信、加解密等部分核心模块:

芯来自研的RISC-V CPU:可根据具体需求选择N300(普通系统)、NS300(安全防护更高)以及NA300(汽车电子)

MAILBOX:HOST访问HSM内部资源的唯一通道

EFUSE:密钥等信息安全存储

BROM:HSM第一级BootLoader

CRYP:对称加解密模块

ACRYP:非对称加解密模块

HASH:哈希算法模块

TRNG:真随机数生成模块

密钥管理

加解密运算

哈希计算

eFuse烧写

密钥生成

提供模版配置文件,一键加密打包脚本以及生成相配套的eFuse初始化文件

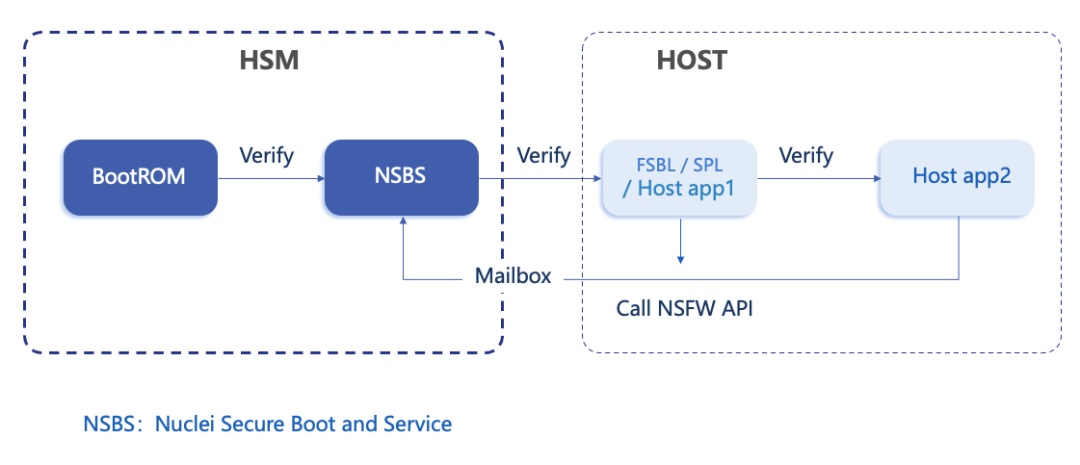

支持两级安全启动全流程仿真

FPGA环境下支持和仿真环境相同的原始固件

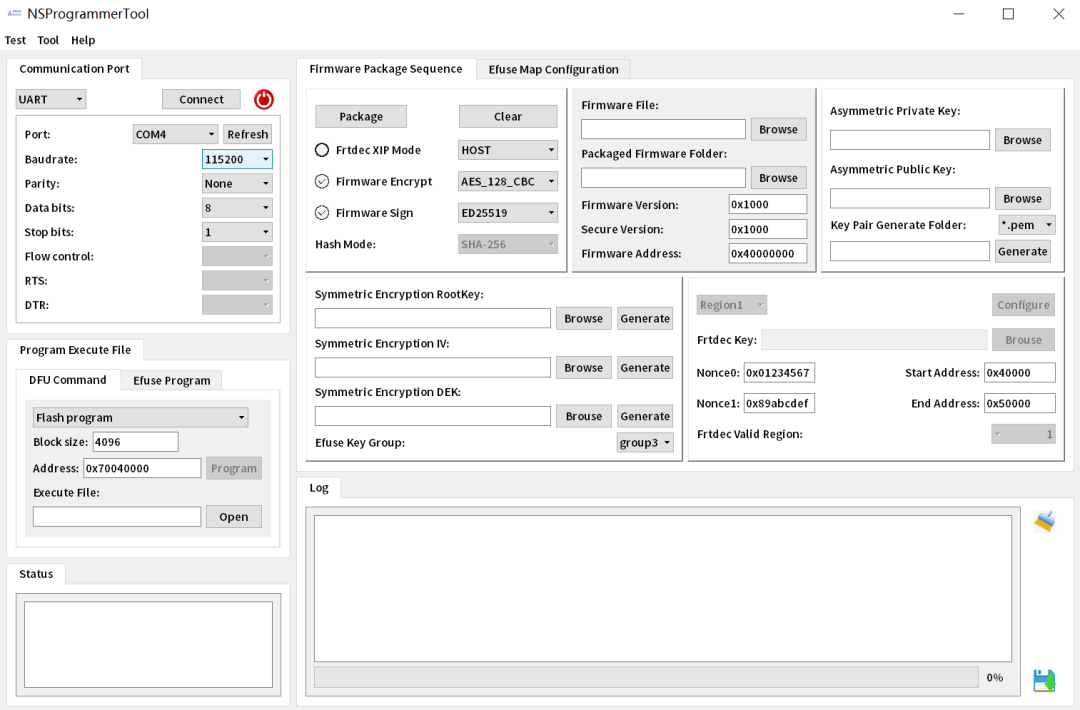

提供功能完善的上位机工具,支持生成并烧写eFuse配置文件和打包原始固件,不需要额外的烧写工具

非对称认证,主要用于验签:

芯片厂商和系统厂商拥有各自独立的密钥对;

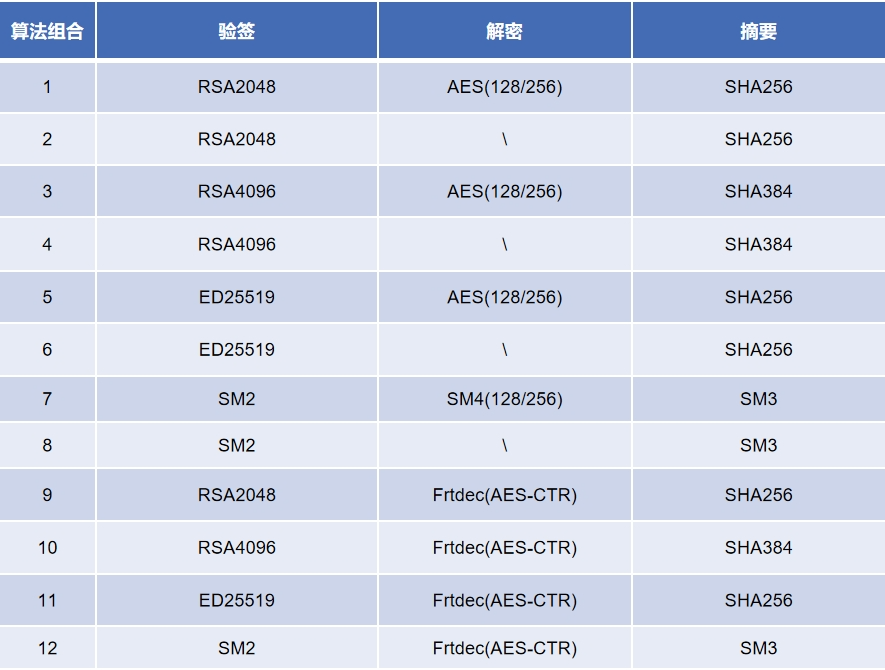

支持ED25519, RSA2048/4096以及国密SM2验签算法

芯片厂商和系统厂商各自拥有根密钥

支持AES和国密SM4加解密算法

支持RFC3394定义的AES以及GB/T 36624-2018定义的SM4密钥封装算法,提供更高的安全性能

固件打包功能:

支持两级镜像的打包,多级密钥生成

根据UI界面的配置,生成固件头,加密固件,计算固件摘要和签名,生成打包后二进制文件

生成eFuse配置文件

DFU:烧写或者擦除Nor Flash指定某个扇区以及整片,可以实现在线更新固件

eFuse烧写:单bit或者单word烧写,根据生成或者指定的eFuse配置文件进行批量烧写

支持备份密钥

支持密钥销毁

支持固件版本管理

支持限制软件bootloader,提高安全性;

开发模式

量产模式

支持备份镜像,支持多种加解密算法

信息安全的保护是当下电子产业必不可少的元素。RISC-V作为开放标准的、可扩展的指令集能够进一步提高了HSM子系统的灵活性以及高度可定制性,同时为国产自主提供了更稳定的基础。芯来科技背靠中国本土市场,将不断完善以芯来RISC-V CPU为核心的HSM安全方案特性,致力于打造完整的信息安全解决方案,配合行业的演进以及发展趋势,目前HSM安全方案已经落地,并且正式进入了商用阶段。

▼往期精彩回顾▼

芯来科技发布最新NS100内核IP,完善全系列信息安全内核布局

芯来发布NI系列内核,NI900矢量宽度可达512/1024位

芯来科技携手西门子EDA,推进RV CPU Trace完整解决方案

芯来携手战略伙伴为RISC-V CPU IP提升DFT可测试性设计

芯来科技荣获中国开放指令生态(RISC-V)联盟“IP先锋奖”

亮相国际舞台 | 芯来RISC-V CPU IP北美峰会引关注

兆易创新推出Wi-Fi 6 MCU,芯来RISC-V内核再赋能