喜欢4次

团队编号:CICC1849

团队名称:能用就行队

学校:安徽工业大学

团队成员:高志强,叶颖,汪志泉

指导老师:王玲玲

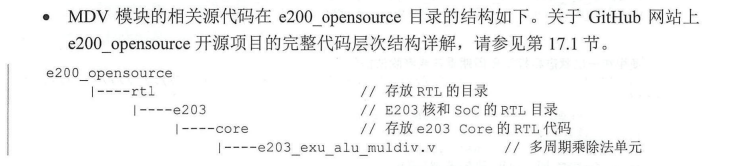

加法器与其他的ALU子单元复用共享的运算数据通路,硬件实现非常节省面积,是一种相当低功耗的实现方式,但其性能十分低下。

对于乘法操作,为了减少乘法操作所需的周期数, MDV 对乘法采用基 (Radix-4 ) 的Booth 编码,进行一次乘法操作需要17个时钟周期。

对于除法操作,采用普通的加减交替法,同样对于无符号乘法进行一位符号扩展后统一当作有符号数进行运算,另外,由于加减交替法迭代所得的结果存在着1比特精度的问题,因此还需要额外3个周期判断是否需要进行余数的矫正,和额外2个周期的商和余数矫正,最终得到完全准确的除法结果,总共最多需要 36个时钟周期。

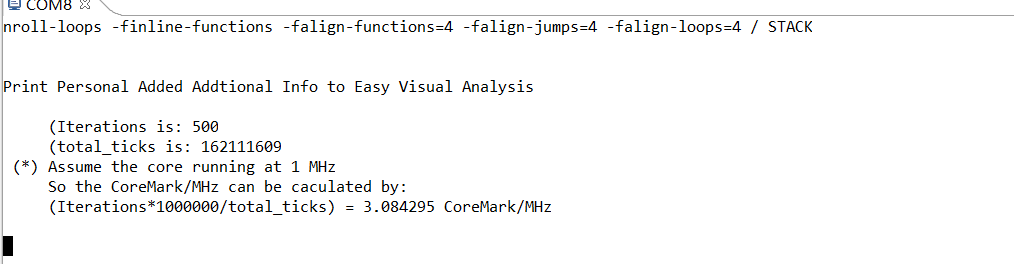

乘除法器优化前跑分约为2.1 CoreMark/Mhz

换用高性能单周期乘除法器后,跑分显著提升