团队编号:CICC6217

团队名称:会吹风的亚索~

学校:杭州电子科技大学

团队成员:李浩、刘坚、赵博涵

指导老师:申东升

E203V2乘法器所在模块为e203_exu_alu_muldiv.v,其中包含乘法和除法两大块,这里仅对乘法模块进行解读。

乘法模块首先进行booth编码,其目的为方便两个有符号数相乘,有关booth编码见以下链接:

https://zhuanlan.zhihu.com/p/143802580

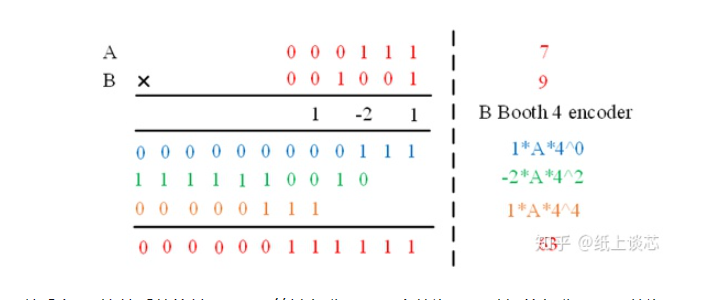

以上述为例,采用基4的booth编码可以方便带符号数相乘同时还将部分和运算次数降低至原来的一半,如采用普通二进制乘法,两个6bit数相乘将会有6个部分和,而采用boothcode编码后,仅会出现0,A,-A,2A,-2A五种部分和运算结果,对于0,A很方便运算,2A次之,-A和-2A较复杂,而结合E203V2的数据通道中的加法运算单元可得加法器的输入没有进位,而进行减法器运算时,进位输入为1,此时完美解决了-A和-2A的问题,只需将运算单元由加法器转为减法器,同时将原来的操作数按位取反即可。

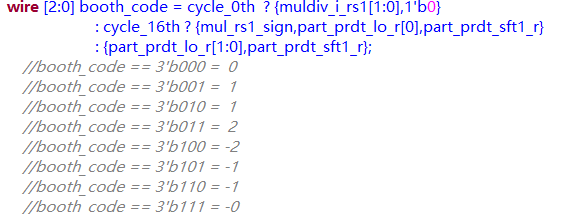

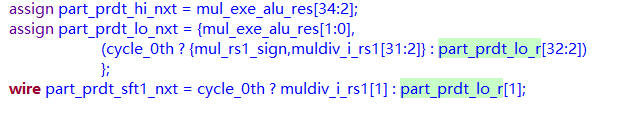

E203V2多周期运算单元中乘法器booth编码具体如下:

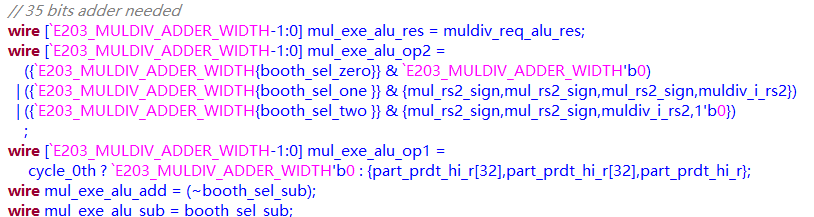

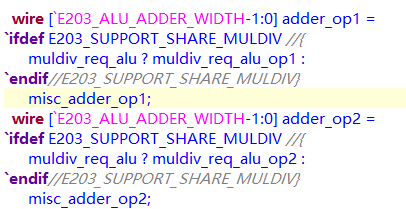

进行乘法运算时所调用的加法器的两个操作数具体如下:

这里把乘法器的操作数1作为booth编码对象,乘法器所调用的加法器的操作数1为高位部分和,加法器的操作数2为乘法器操作数2的(0,A,2A,-A,-2A)结果,另外,boothcode的最高位为1时便涉及到负数运算即减法,此时便将原操作数按位取反即可,结合乘法器的进位输入便可解决,以下为数据通道中加法器的操作数选择:

此外,在乘法器运算中部分和作为加法器的一个操作数,两个32位数相乘,则如前所述共有16个部分和

高位部分和每运算一次后右移两次,并且参加下一次部分和的运算,而低位部分和从第一次开始便从32位寄存器高位开始右移两位,以此类推,进行16次加法运算后,高位部分和已经算出来了,而低位部分和刚好右移到寄存器的最低位,最后还需一个时钟周期输出乘法器的运算结果。

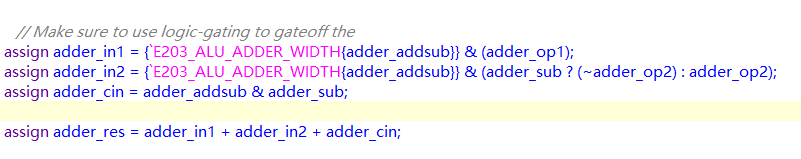

同时,可以看到E203V2乘法器为了实现低功耗小面积的目标,与alu_regular模块内的加法器共享硬件单元,数据通道中加法器的操作数选择部分源码如下所示:

由此可以看出乘除法器调用加法器的优先级最高,当乘除法器运算时,加法器不能被其他地方调用,而是等待乘除法器完成。