一、队伍介绍

报名编号:CICC2740

团队名称:管他三七二十一

学校名称:华中科技大学

队伍成员:龚绎天、李泽立、王欣倓

指导老师:王超

大家好,本篇是我们队伍的第二篇分享,主要内容是全流程(保姆级)介绍一下如何基于Nuclei DDR200T开发板移植E203,完成BIN文件的生成。水平有限,如有错误,欢迎大家批评指正。

二、主要内容介绍

(1)首先到芯来Github上下载蜂鸟e203 soc的源码https://github.com/riscv-mcu/e203_hbirdv2

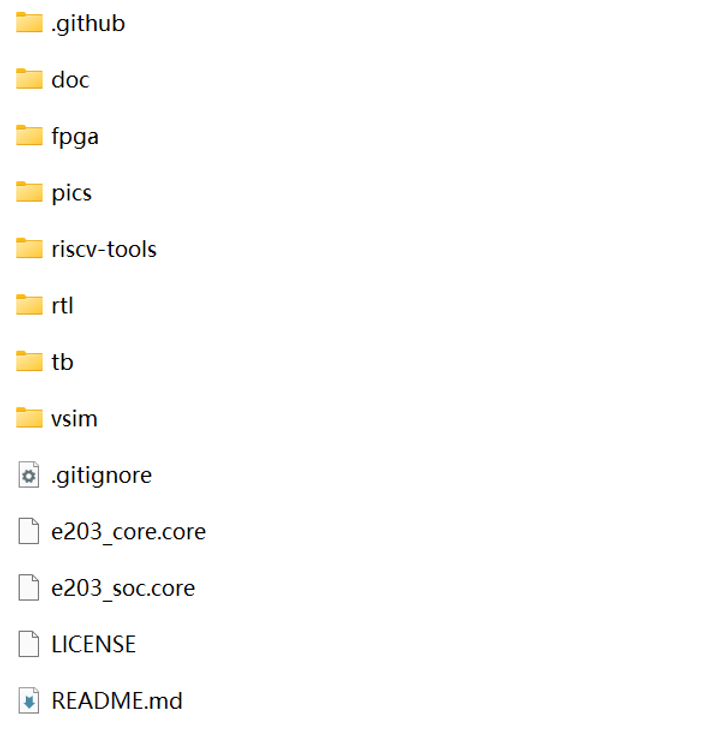

以下为其文件目录

(2)建立vivado工程

我使用的vivado版本为2020.2版本,其他vivado版本操作基本一致

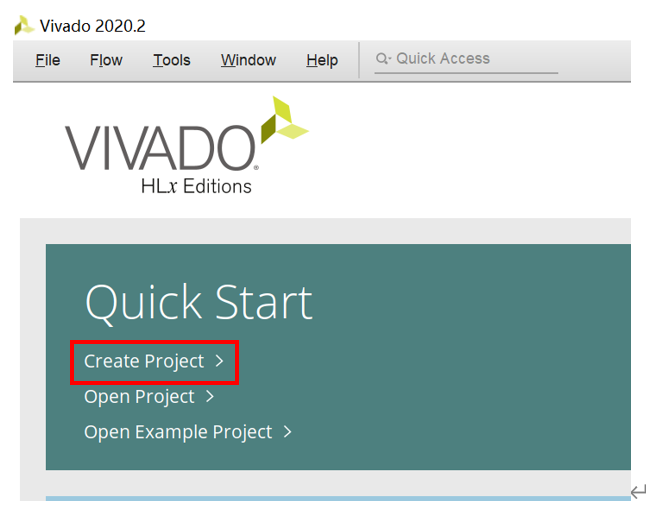

首先创建一个project

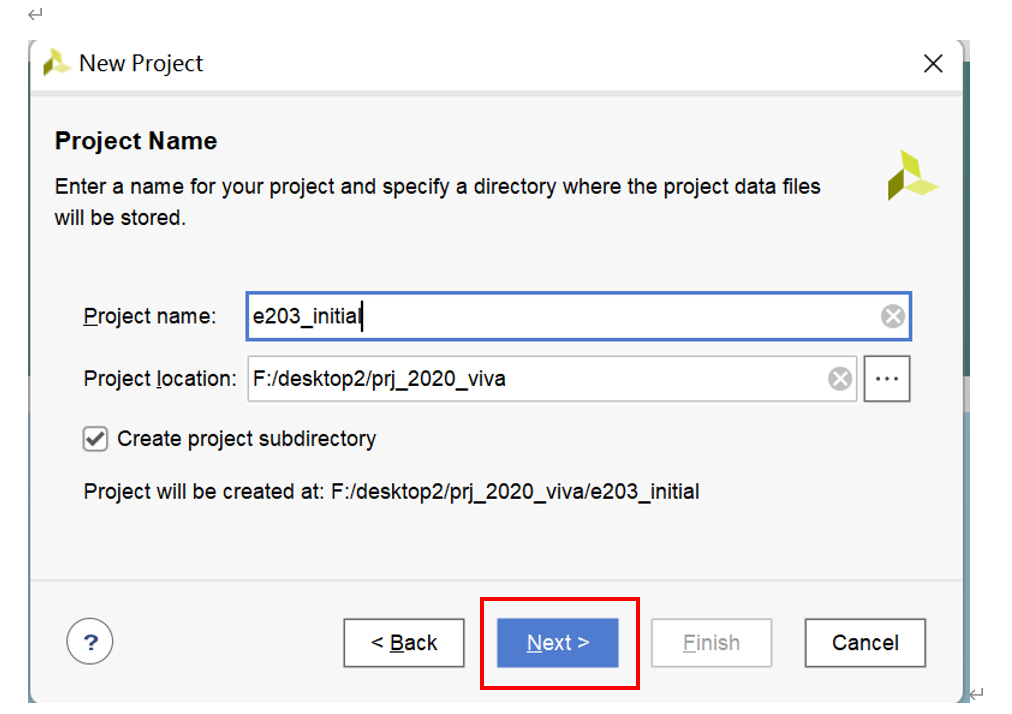

起好名字后点击下一步

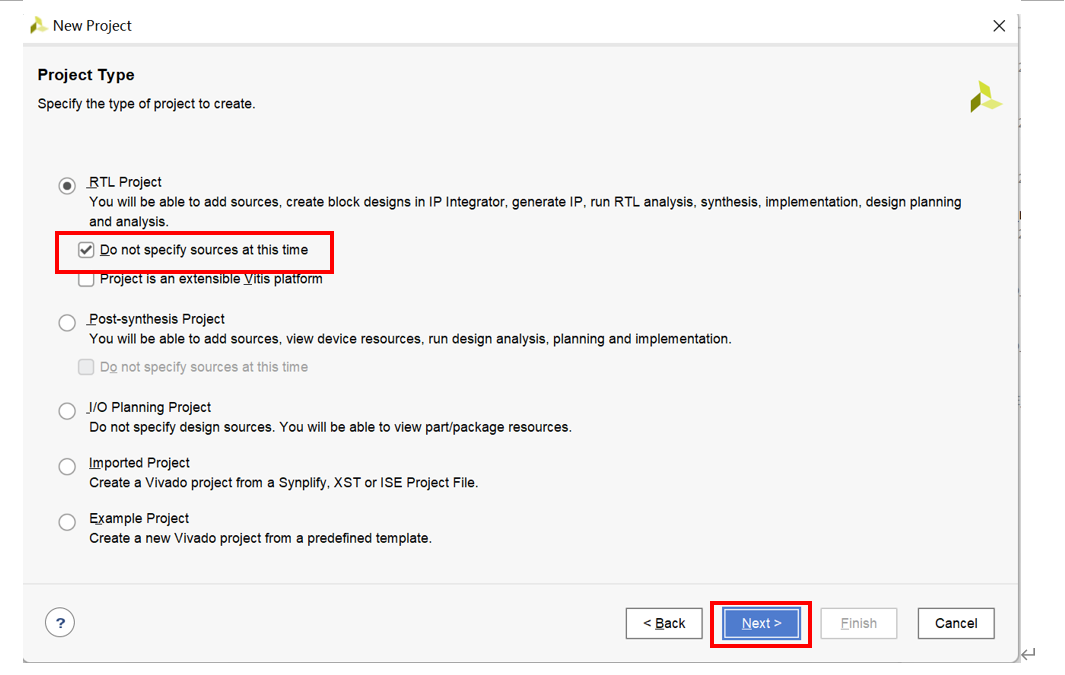

这里选择RTL project ,勾选此时不指定源文件,注意下一个“project is an extensible vitis platform”,在2019.2以前的版本是没有的,不用管,2019.2以后的版本,不勾选。点击next

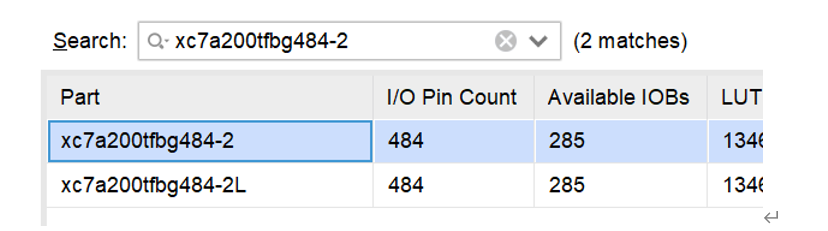

这一步选择器件 xc7a200tfbg484-2, 点击next,下一个界面直接点击右下角finish,完成创建。

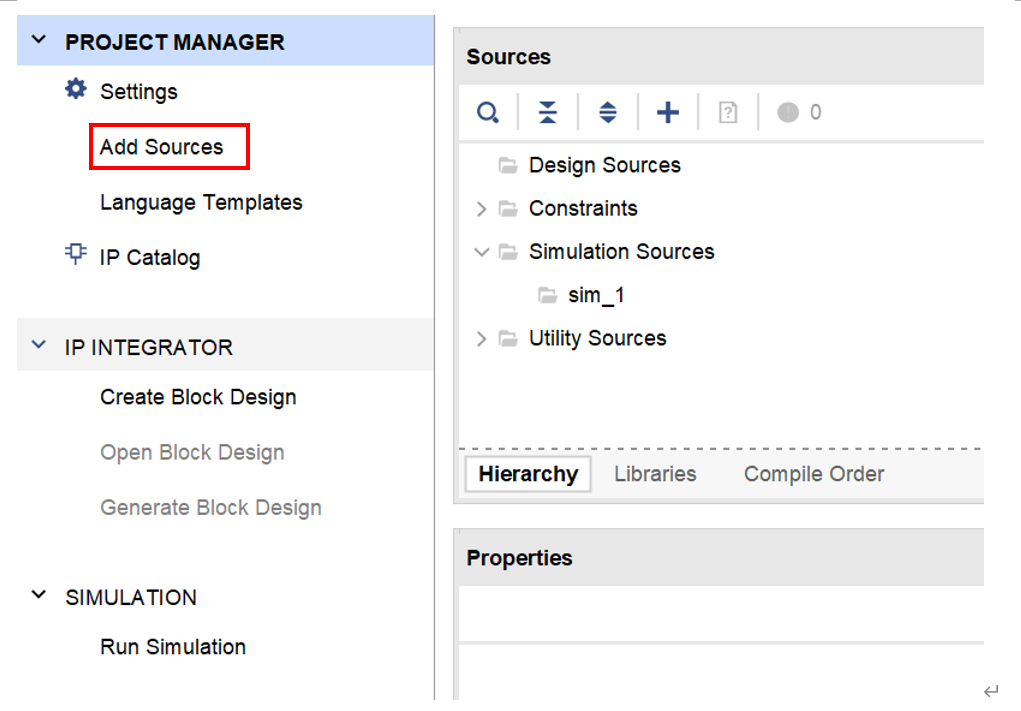

选择add source,

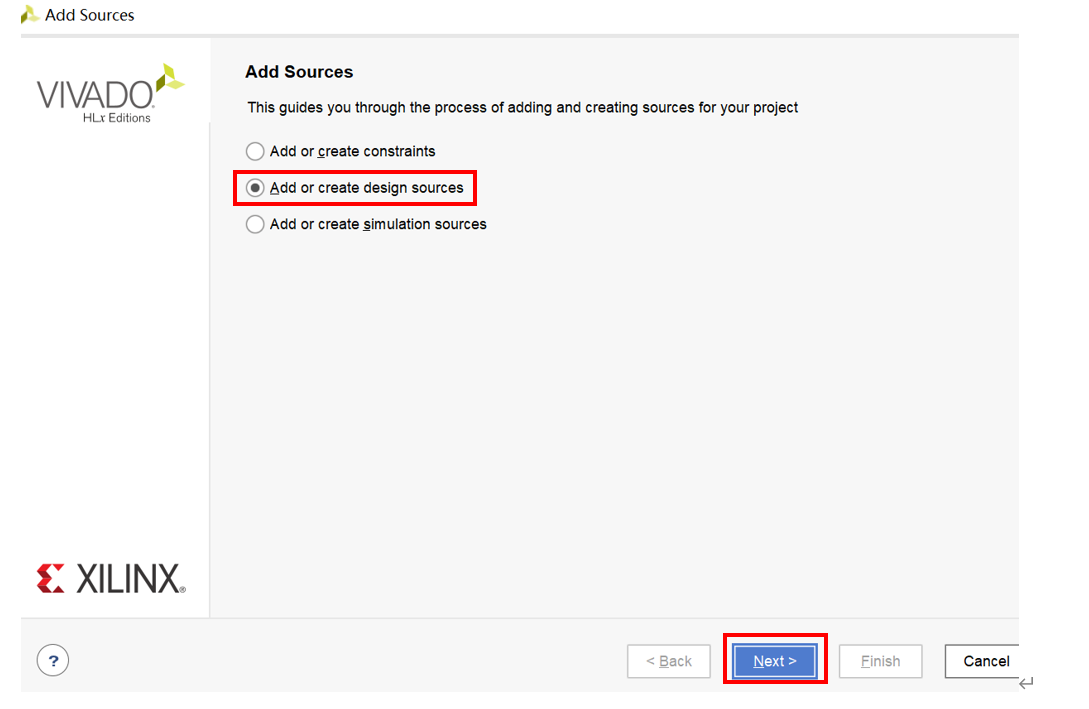

选择 add design source,点击next

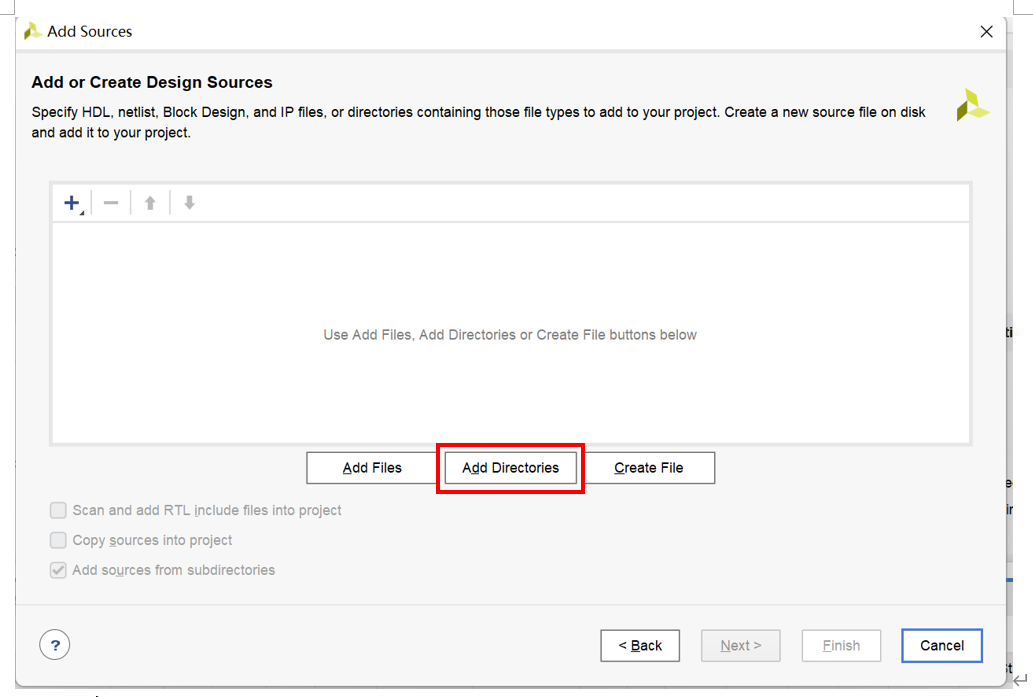

这里选择add directions

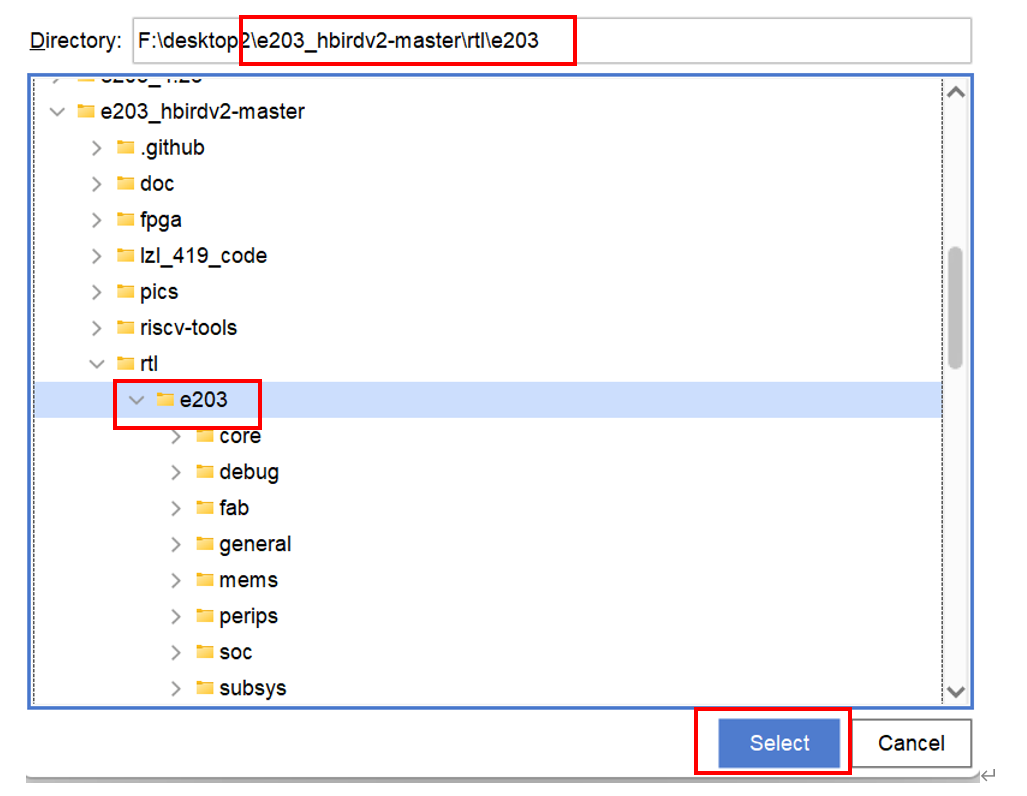

选择“e203”文件夹,点击select

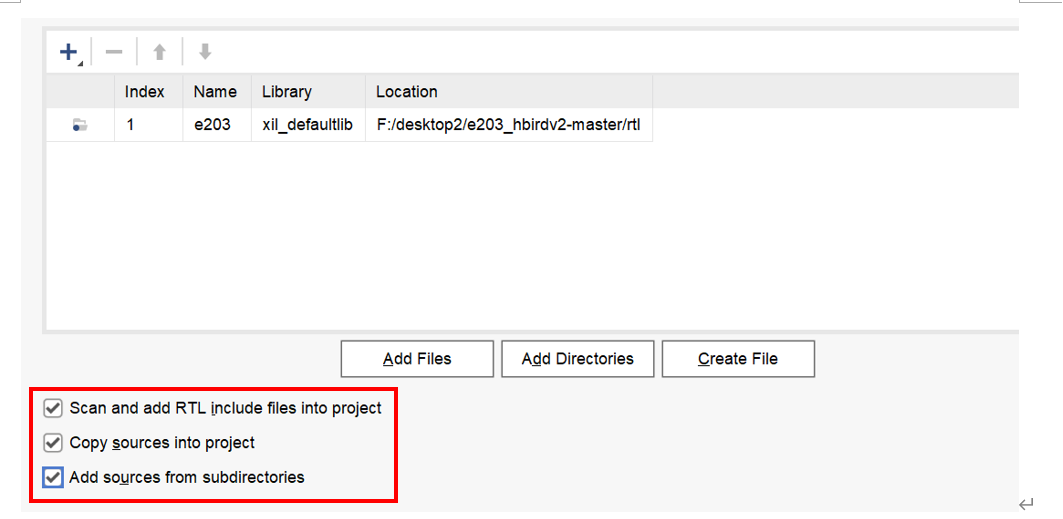

点击select之后 回到此界面,勾选此三项,这个是把添加的文件复制到project文件夹下,这样方便project写好之后整体打包发送。

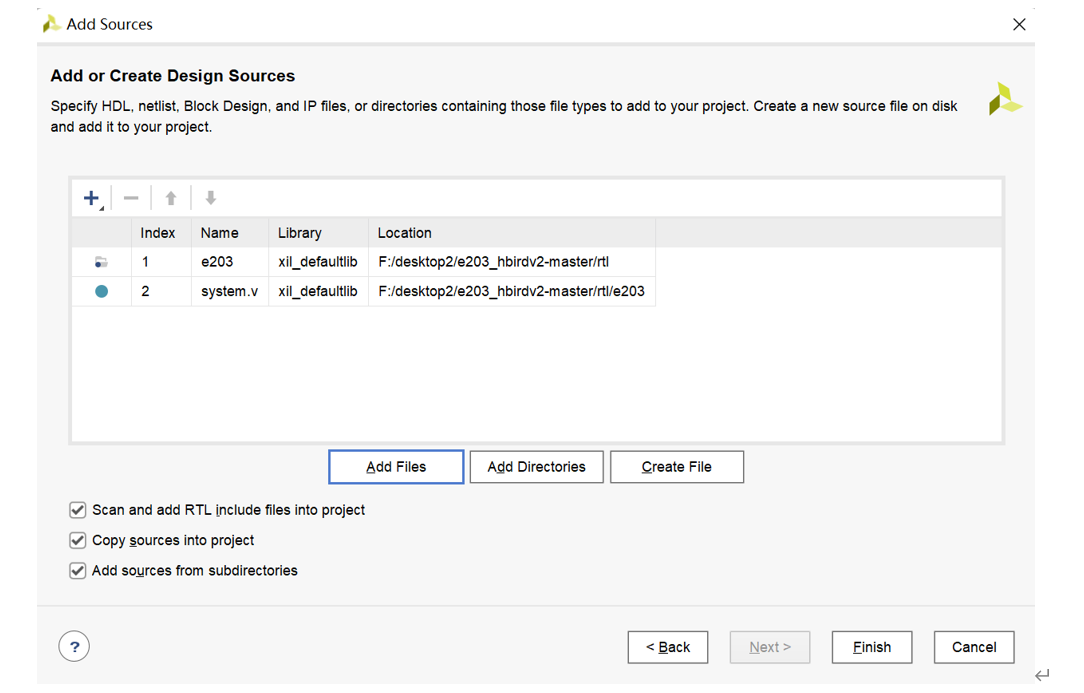

然后点击add source,添加目录在e203_hbirdv2-master\fpga\ddr200t\src的system.v文件

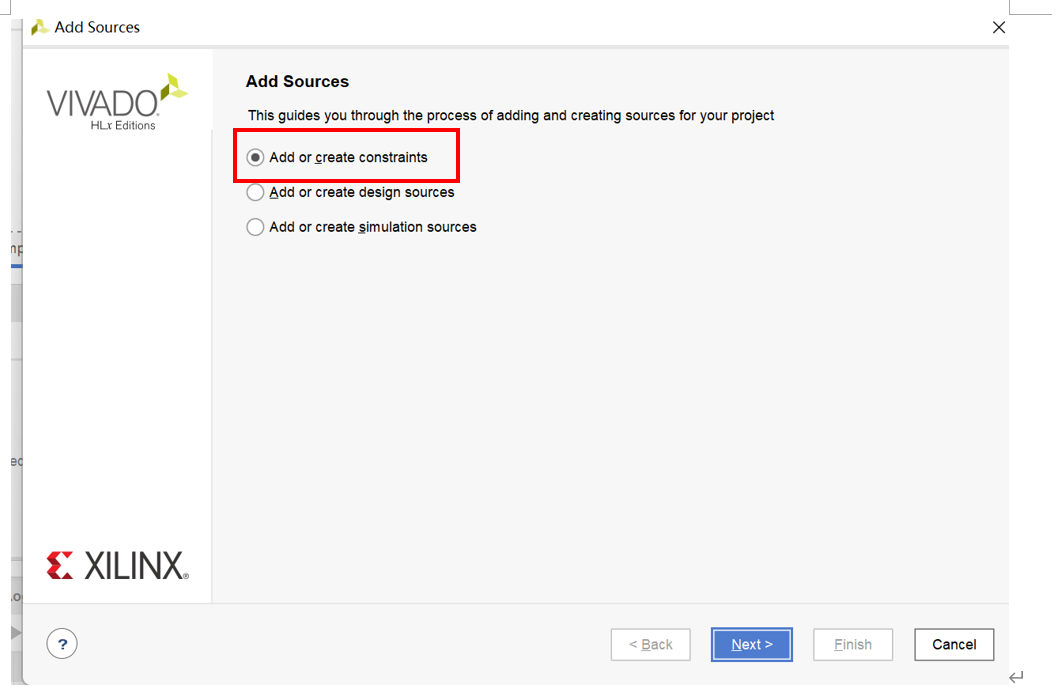

点击finish, 然后再add source,选择添加约束文件

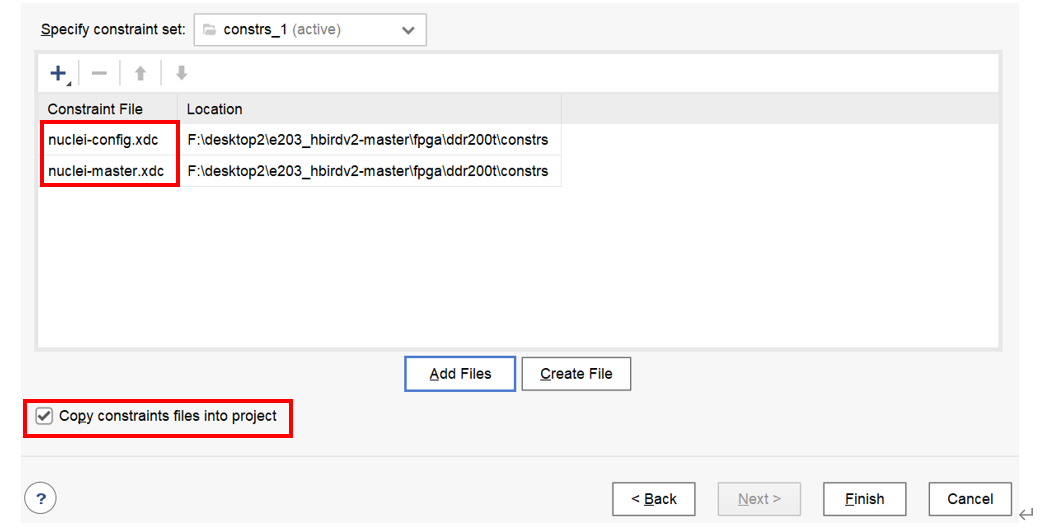

添加目录在e203_hbirdv2-master/fpga/ddr200t/constrs的两个约束文件,同样勾选复制文件到project

点击finish完成文件添加。

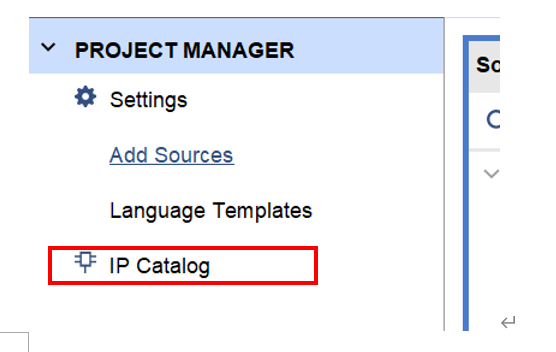

下面进行ip核添加,点击ip catalog

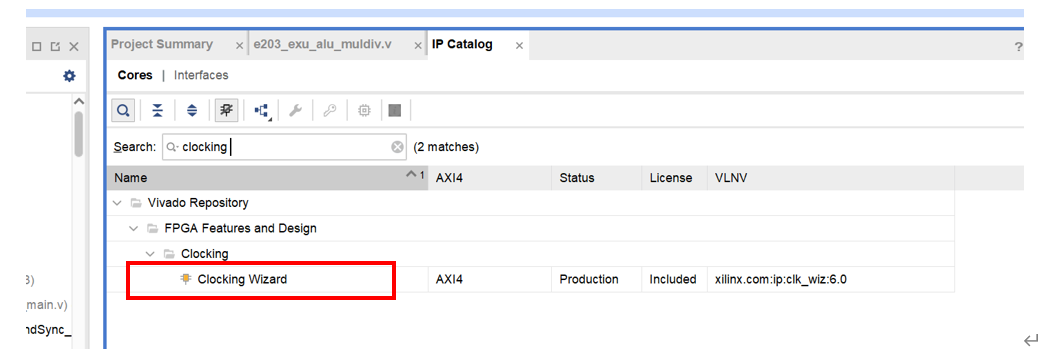

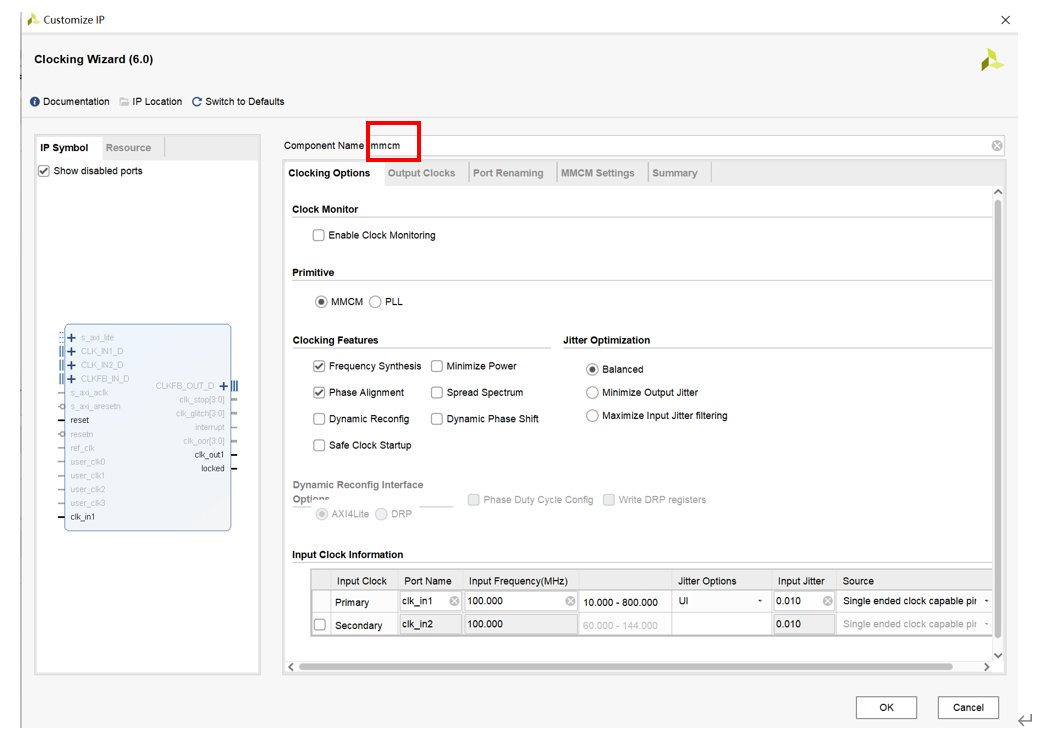

首先是mmcm,在右侧搜索clocking,双击clocking wizard

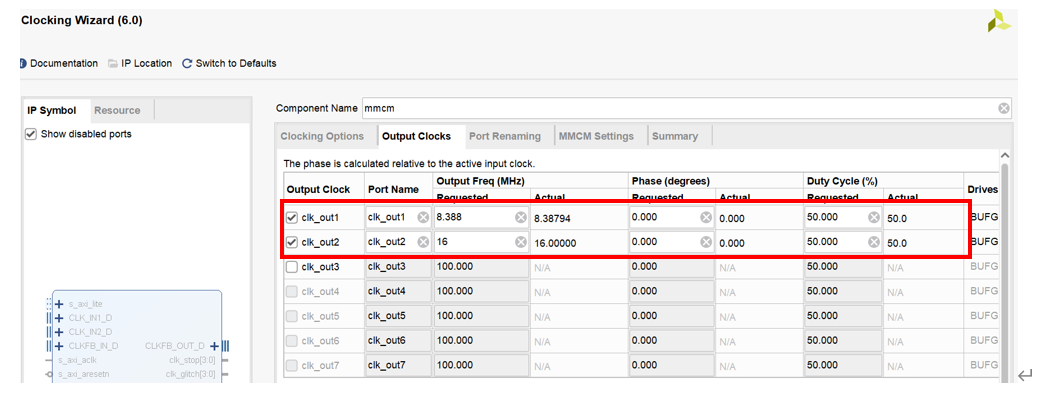

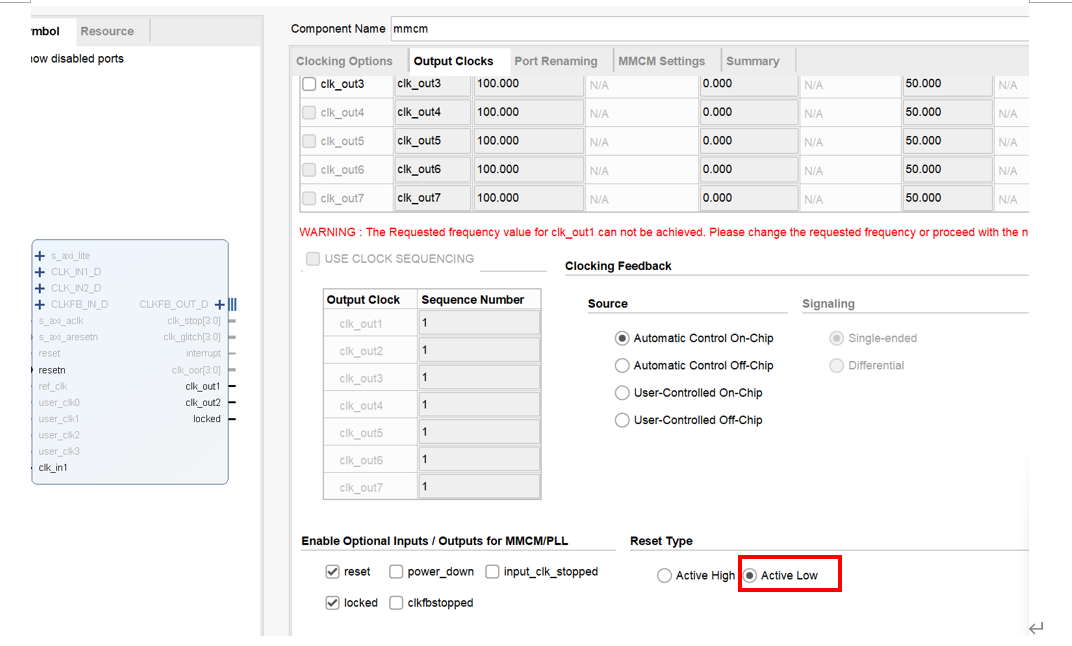

相关配置如下图所示,共三处,其余保持默认,配置完成后点击finish。

选择out of context per IP,点击generate即可

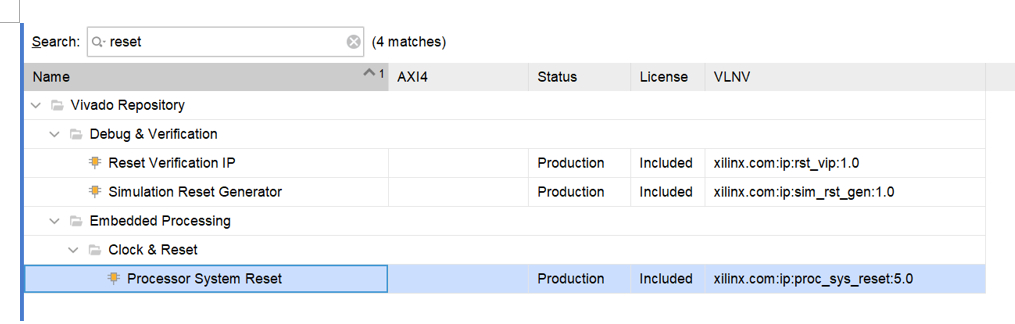

接下来是reset ip,搜索reset,双击选择processor system reset

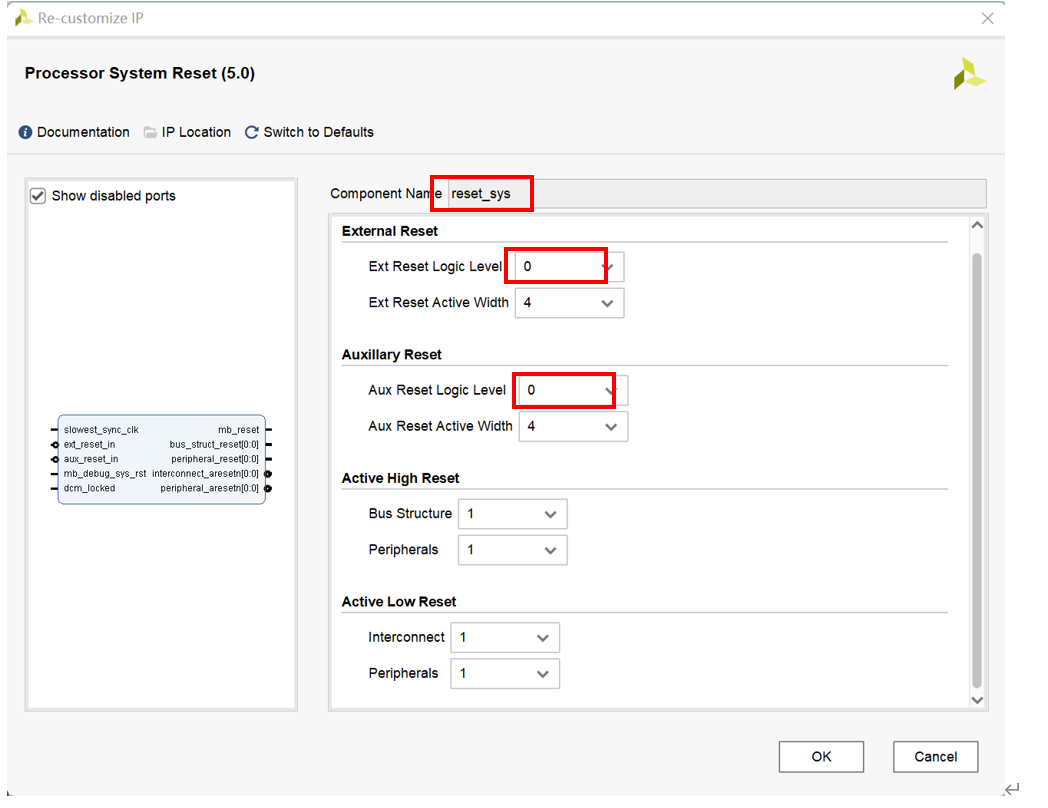

配置与下图保持一致,共修改3处,其余默认,注意修改名称

同样选择out of context per IP,点击generate即可。

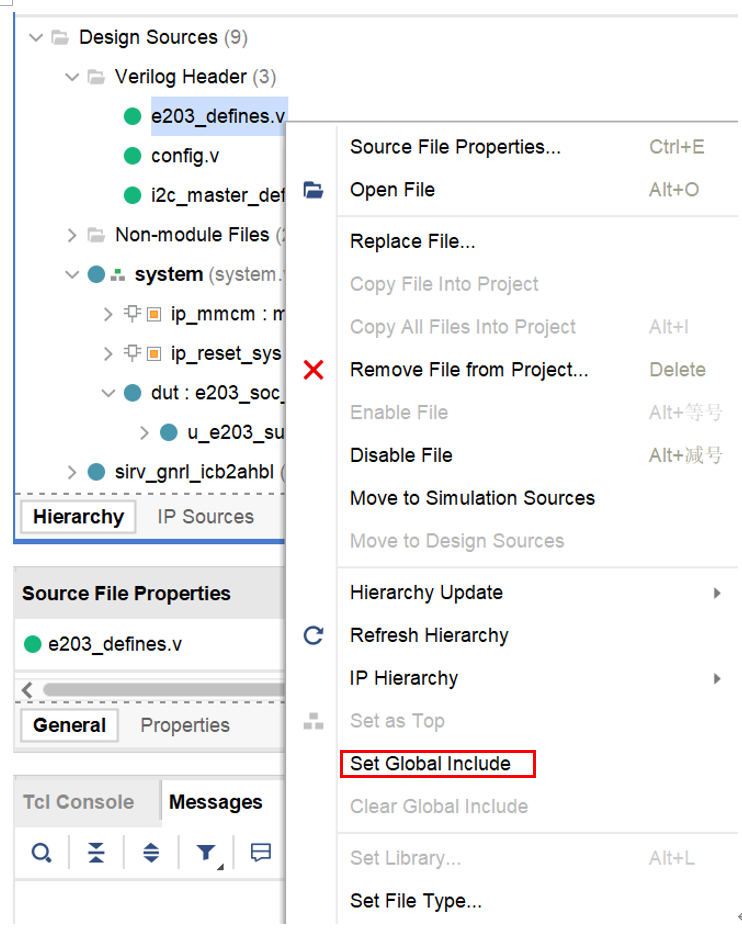

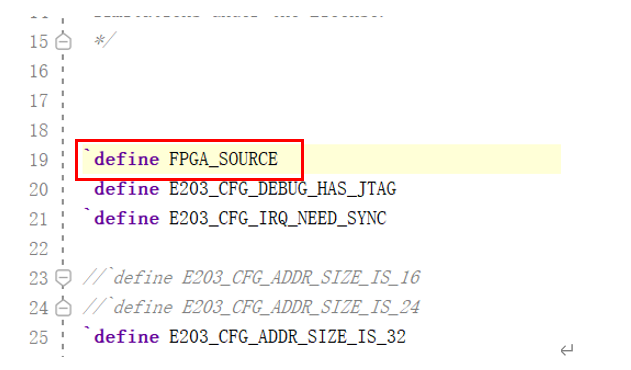

在source中的verilog header中找到e203_define.v,右键选择set global include,然后打开config.v,在其中添加一句 `define FPGA_SOURCE,防止报错。

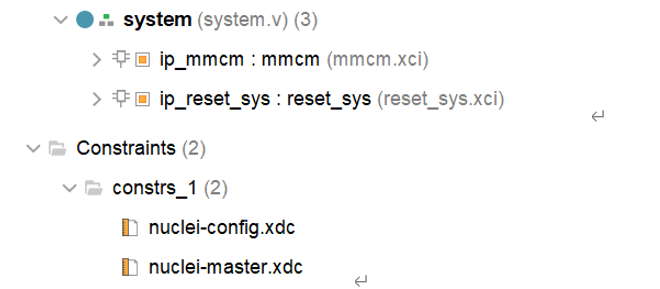

上述步骤完成后,确保system.v文件设置为top文件,确保两个约束文件都已添加,IP核名称正确,如下图所示

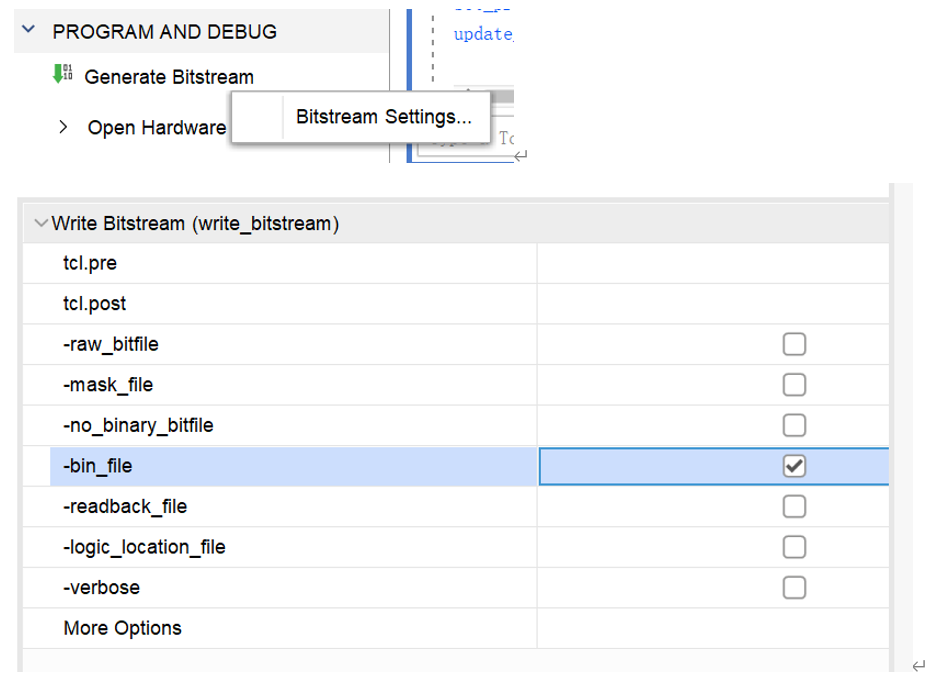

右键generate bitstream,然后点击bitstream settings,勾选bin files

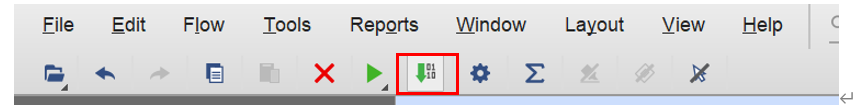

点击ok,然后点击下图中的generate bitstream

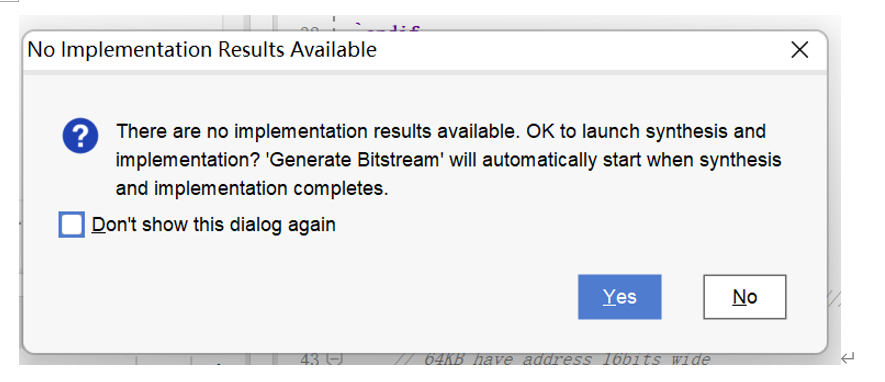

点击yes

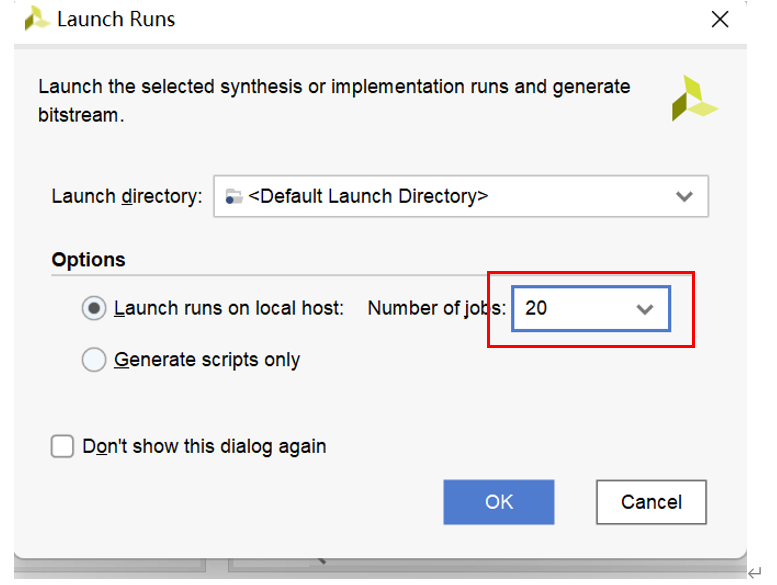

下图中选择最大线程数,点击ok,等待完成即可,大约需10到20分钟。

完成之后,在projectname\projectname.runs\impl_1文件夹下找到system.bin即为生成的bin文件。