报名编号:CICC1907

团队名称:Hollow-SEKIRO-ARCAEA

学校名称:东南大学

指导老师:刘昊

团队成员:申烁、徐轶凡、林昊

这是我们第八篇分享文章。

我们在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定义其计算种类及多模式选择。有时多种计算可以用同一个IP核实现,举例比较大小模式:

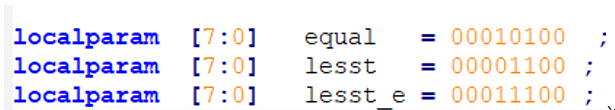

此时会需要模式控制信号,该信号的设置方法参考其文档,如加法是8‘b0,减法是8‘b1,该规则对乘加/减、加减都成立。有的IP核输入模式较多,如其中比较计算的可配置模式可以进行8种计算,但我们设计的模块内只用到三种:

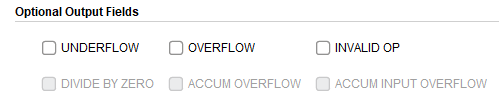

当比较结果成立时出1,不成立出0,不可配置时可以输出更多结果,如数据不可比较(NAN)时将低第四位置高。须注意,比较计算不存在上溢下溢,只有无效操作数这一种异常状态。

不同的计算存在不同的异常,如加减乘存在溢出,除法存在除零异常等。

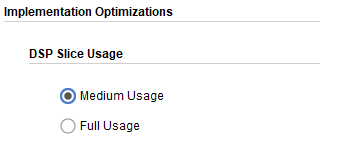

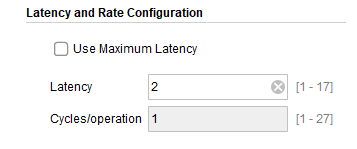

另一个设置要点是时序的优化问题,在优化选项中可以选择是否使用DSP、使用多少,电路优化可以选择以资源或性能为目标;但更重要的是延迟周期数,周期数设置的越高,时序更能得到优化,每种计算单周期完成的最大延迟都有所不同,除法、开方可以设置高达29个周期的延迟,而比较最大仅需要三个周期,参考了其他RISC v架构的处理器,我们将乘除、乘加、开方设置为多周期,其他的则是单周期。以下以乘法IP为例,介绍各个选项。

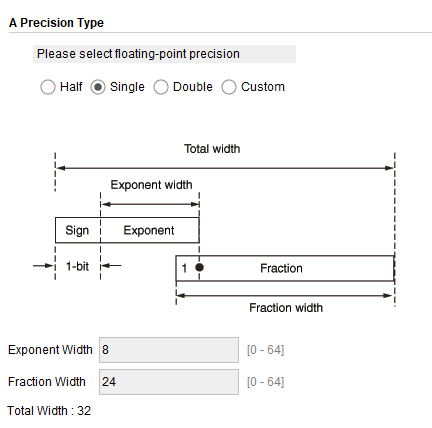

IP核的输入数据格式也是可配置的:

有的IP可以选择是否调用DSP:

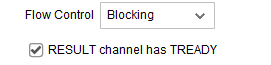

非阻塞模式将取消输入ready和输出valid信号:(输出ready可选择)

以资源或性能作为优化目标也是可选的:

运算周期数也可调,越复杂的计算可选择的最大周期数越大:

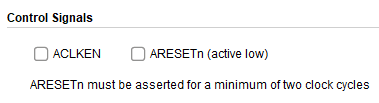

控制信号有时钟使能和复位:

计算异常,不同的计算有不同的异常:

本文介绍的内容是为了完成基础功能:对蜂鸟E203 RISC-V内核的微架构实现进行一定优化,在添加F拓展的过程中的一些记录。