报名编号:CICC1327

团队名称:301小队

本次板级验证基于vivado.2020.02,完成工程建立,所用FPGA板型为:xc7a200tfbg484-2,主要挑几个上板易错点进行分享。

蜂鸟E203有两个时钟信号:

HCLKGEN(高速时钟生成):主体域为生成高速时钟,频率为16MHZ。可以利用MMCM IP核分频产生。

LCLKGEN(低速时钟生成):主要常开域生成低速时钟,频率为32.768KHZ,但MMCM 无法分频这么小的频率,故将8MHZ(MMCM产生)分频244得到。

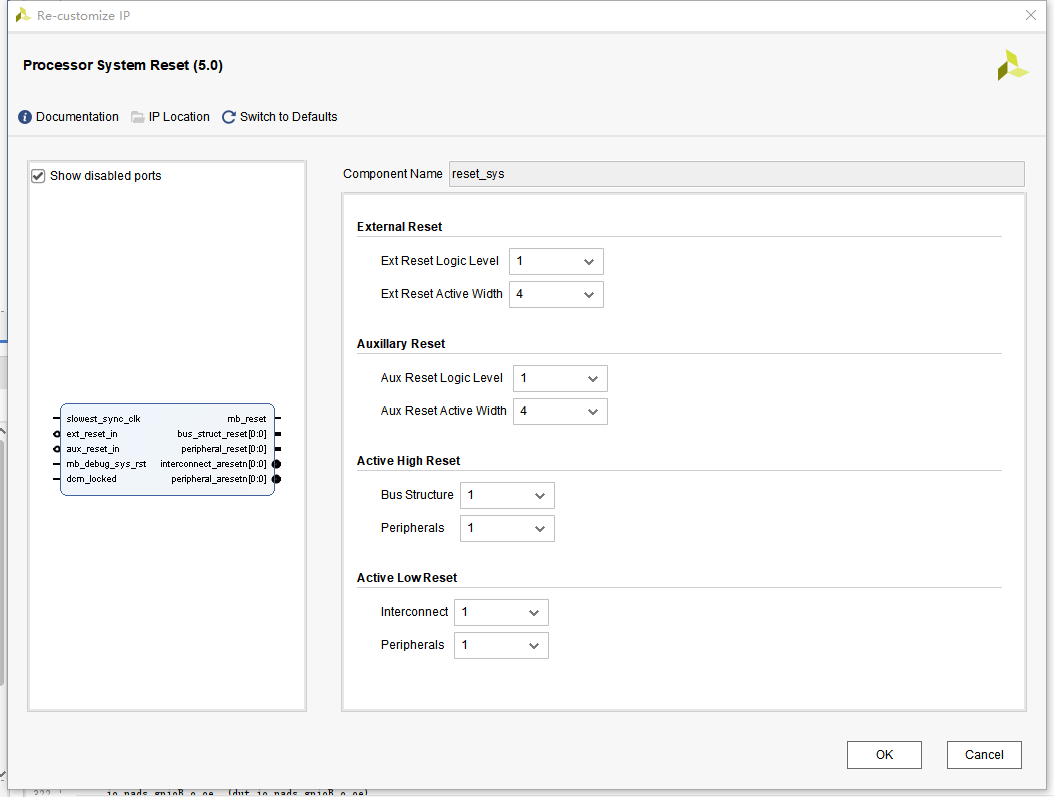

复位IP核如下图进行添加:

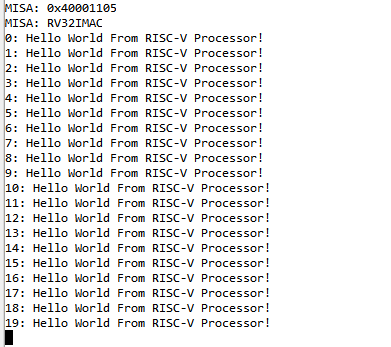

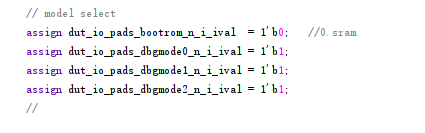

要想使用程序从ITCM中加载,要将dut_io_pads_bootrom_n_i_ival变为1’b0

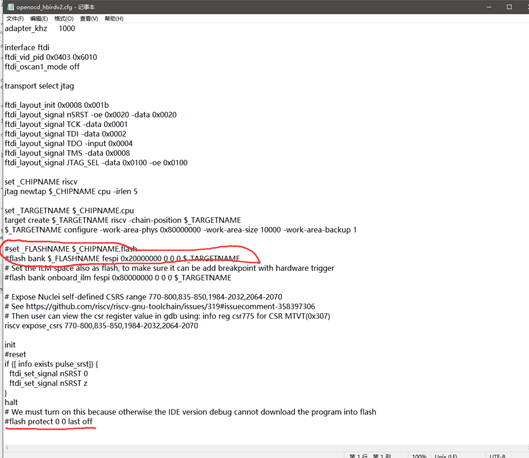

另外与之对应在NucleiStudio IDE中将flash模式注释掉,这样才不会报错,注释如下图所示:

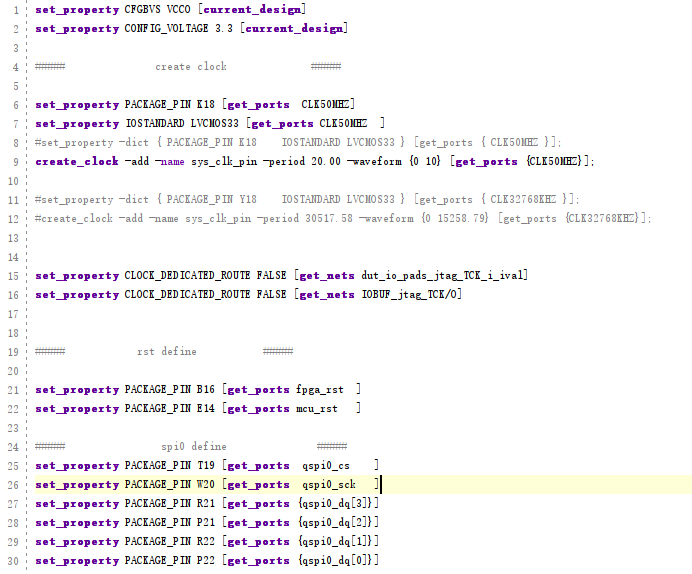

rtl顶层模块有两个复位信号,分别是 fpga_rst 和 mcu_rst,即FPGA开发板自身的复位和为MCU设置的复位,这两个复位通过一个与操作生成一个为SoC使用的复位信号,即SoC复位的条件是这两个复位信号至少有一个生效。当着两个复位键都为1时,从而将电源唤醒,可以设置一个LED观察现象是否烧录至FPGA中,当约束的灯灭时,代表烧录进去。

部分管脚约束如下图所示:

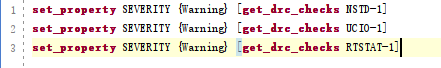

有些管脚不需要约束时,可以采用以下三条脚本命令,这样才不会一直报错: