报名编号:CICC3940

团队名称:树上鸟儿成双队

fcvt.s.d rd, rs1, rs2 //f[rd] = f32f64(f[rs1])

双精度向单精度浮点转换(Floating-point Convert to Single from Double). R-type, RV32D and RV64D.

把寄存器 f[rs1]中的双精度浮点数转化为单精度浮点数,再写入 f[rd]中。

fcvt.d.s rd, rs1, rs2 //f[rd] = f64f32(f[rs1])

单精度向双精度浮点转换(Floating-point Convert to Double from Single). R-type, RV32D and RV64D.

把寄存器 f[rs1]中的单精度浮点数转化为双精度浮点数,再写入 f[rd]中。

fsqrt.d rd, rs1, rs2 //f[rd] =sqrt(f[rs1])

双精度浮点平方根(Floating-point Square Root, Double-Precision). R-type, RV32D and RV64D.

将 f[rs1]中的双精度浮点数的平方根舍入和写入 f[rd]。

fle.s rd, rs1, rs2 //x[rd] = f[rs1] ≤ f[rs2]

单精度浮点小于等于(Floating-point Less Than or Equal, Single-Precision). R-type, RV32F and RV64F.

若寄存器 f[rs1]中的单精度浮点数小于等于 f[rs2]中的单精度浮点数, 则在 x[rd]中写入 1,反之写 0。

flt.s rd, rs1, rs2 //x[rd] = f[rs1] < f[rs2]

单精度浮点小于 (Floating-point Less Than, Single-Precision). R-type, RV32F and RV64F.

若寄存器 f[rs1]中的单精度浮点数小于 f[rs2]中的单精度浮点数, 则在 x[rd]中写入 1,反之写0。

fle.d rd, rs1, rs2 //x[rd] = f[rs1] < f[rs2]

双精度浮点小于 (Floating-point Less Than, Double-Precision). R-type, RV32D and RV64D.

若寄存器 f[rs1]中的双精度浮点数小于 f[rs2]中的双精度浮点数, 则在 x[rd]中写入 1,反之写0。

fle.d rd, rs1, rs2 //x[rd] = f[rs1] < f[rs2]

双精度浮点小于 (Floating-point Less Than, Double-Precision). R-type, RV32D and RV64D.

若寄存器 f[rs1]中的双精度浮点数小于 f[rs2]中的双精度浮点数, 则在 x[rd]中写入 1,反之写0。

feq.s rd, rs1, rs2 //x[rd] = f[rs1] == f[rs2]

单精度浮点相等(Floating-point Equals, Single-Precision). R-type, RV32F and RV64F.

若寄存器 f[rs1]和 f[rs2]中的单精度浮点数相等, 则在 x[rd]中写入 1,反之写 0。对于FLT,FLE和FEQ指令,如果任何一个操作数位NaN,则结果为0。对于FLT和FLE指令,如果任意一个操作数属于Nan,则需要在fscr寄存器中产生NV异常标志。对于FEQ指令,如果任意一个操作数属于Signaling-NaN,则需要在fcsr寄存器中产生NV异常标志。

feq.d rd, rs1, rs2 //x[rd] = f[rs1] == f[rs2]

双精度浮点相等(Floating-point Equals, Double-Precision). R-type, RV32D and RV64D.

若寄存器 f[rs1]和 f[rs2]中的双精度浮点数相等, 则在 x[rd]中写入 1,反之写 0。对于FLT,FLE和FEQ指令,如果任何一个操作数位NaN,则结果为0。对于FLT和FLE指令,如果任意一个操作数属于Nan,则需要在fscr寄存器中产生NV异常标志。对于FEQ指令,如果任意一个操作数属于Signaling-NaN,则需要在fcsr寄存器中产生NV异常标志。

fcvt.w.s rd, rs1, rs2 //x[rd] = sext(s32f32(f[rs1]))

单精度浮点向字转换(Floating-point Convert to Word from Single). R-type, RV32F and RV64F.

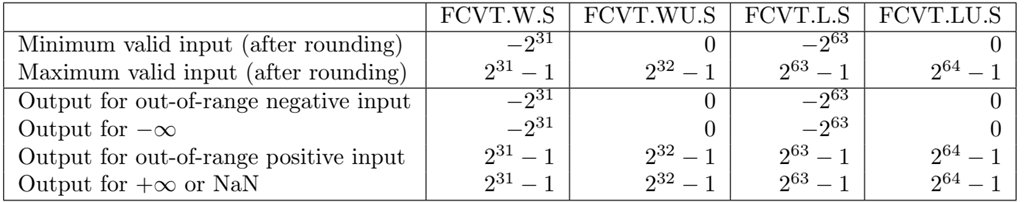

把寄存器 f[rs1]中的单精度浮点数转化为 32 位二进制补码表示的整数,再写入 x[rd]中。由于浮点数表示范围远远大于整数,且浮点数存在一些特殊表示,比如无穷大和NaN等,下表是一些浮点转化整数时候的一些特殊情况。

fcvt.wu.s rd, rs1, rs2 //x[rd] = sext(u32f32(f[rs1]))

单精度浮点向无符号字转换(Floating-point Convert to Unsigned Word from Single). R-type,RV32F and RV64F.

把寄存器 f[rs1]中的单精度浮点数转化为 32 位无符号整数,再写入 x[rd]中。

fcvt.l.s rd, rs1, rs2 //x[rd] = s64f32(f[rs1])

单精度浮点向长整型转换(Floating-point Convert to Long from Single). R-type, RV64F.

把寄存器 f[rs1]中的单精度浮点数转化为 64 位二进制补码表示的整数,再写入 x[rd]中。

fcvt.lu.s rd, rs1, rs2 //x[rd] = u64f32(f[rs1])

单精度浮点向无符号长整型转换(Floating-point Convert to Unsigned Long from Single). R-type,RV64F.

把寄存器 f[rs1]中的单精度浮点数转化为 64 位二进制补码表示的整数,再写入 x[rd]中。