喜欢1次

报名编号:CICC1764

团队名称:两年半IC练习生

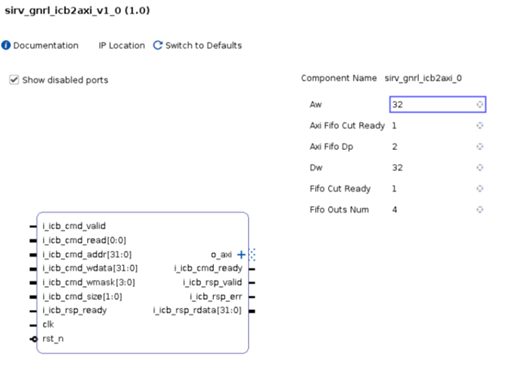

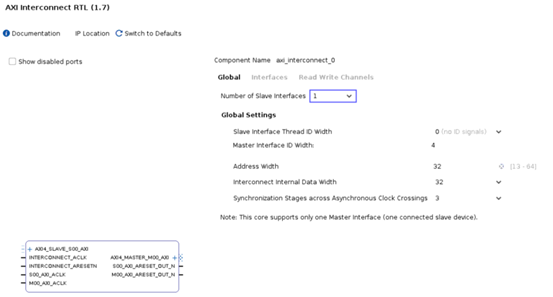

(2)axi_interconnect模块

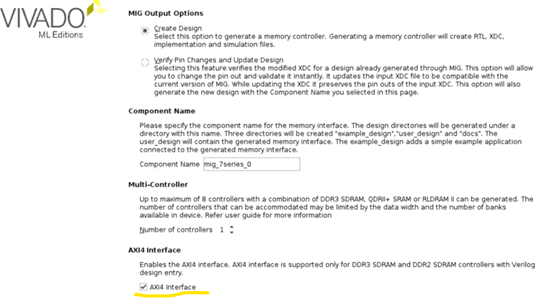

(3)mig模块

mig 的模块配置具体可参考:https://blog.csdn.net/qq_43858116/article/details/123799437

强调一些不同的地方:

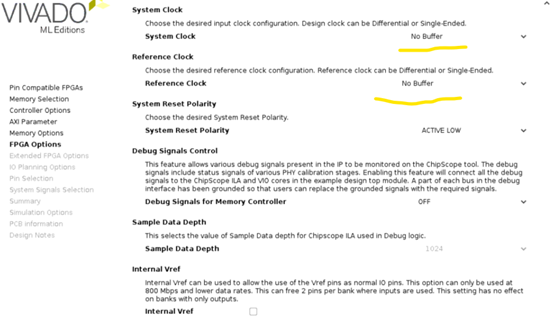

下面AXI4 interface需要勾选,否则产生的模块没用AXI接口。

system clock和reference clock选择no buffer。都采用时钟生成模块mmcm0生成的200M时钟。注意两个时钟的值必须一样,否则mig初始化会出错。

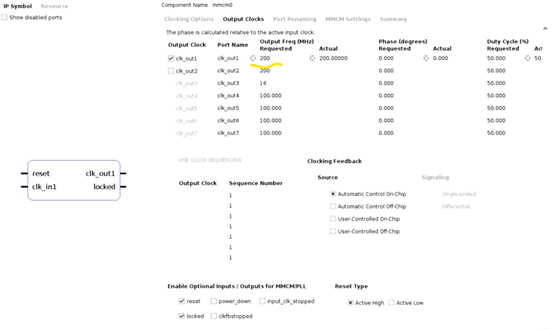

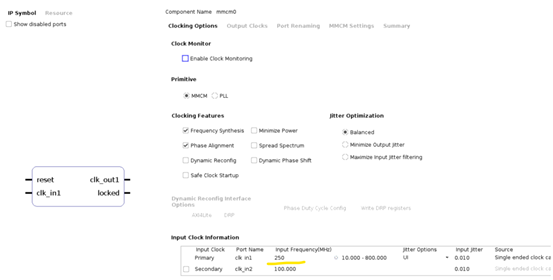

(3)时钟生成模块mmcm0

该模块将系统顶层时钟hfextclk分频或倍频成200M时钟,供mig模块的system_clk和reference_clk使用。