喜欢3次

报名编号:CICC1764

团队名称:两年半IC练习生

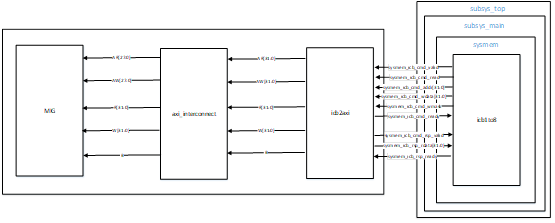

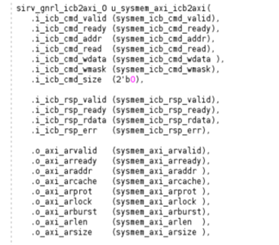

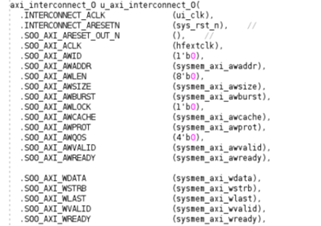

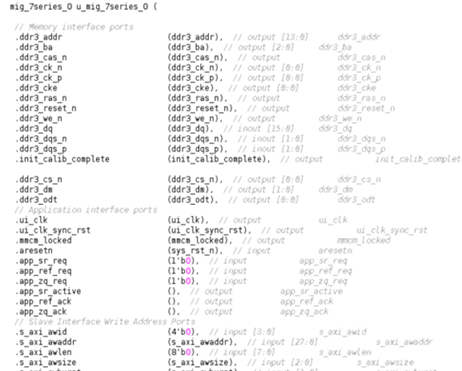

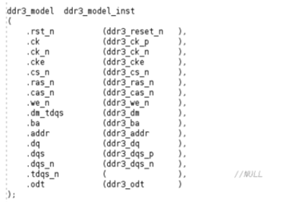

(2)例化DDR3模型(仿真的时候需要用,vivado综合时不需要,直接注释掉),并在design source中添加ddr3_model.sv和ddr3_model_parameters.vh文件。

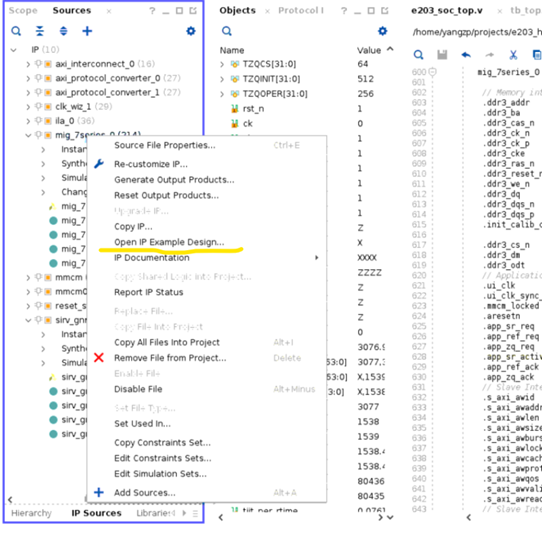

在IP Source中右键点击mig的ip核,然后open ip example design,在新工程文件下会自动生成ddr3模型和相应的文件,在soc_top层中对ddr3模型做例化,并添加相应的文件。

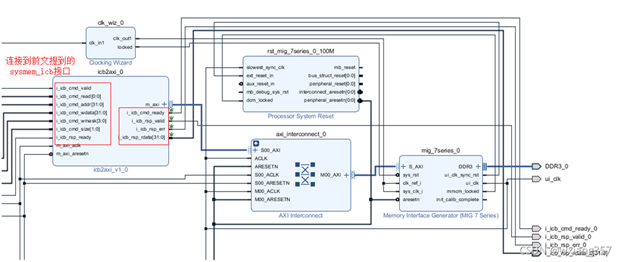

连接总体效果大致如下: