队伍介绍:报名编号:CICC3941 团队名称: 蜡笔小新

这是我们队伍的第一篇帖子

我们原本打算添加的是AHB总线接口的外设,通过阅读e203_subsys_perips.v中的代码,同时发现还有保留的存储空间与空闲接口。但是,由于E203的私有设备总线为ICB总线,且sirv_gnrl_icb.v文件中并没有ICB2AHB总线的模块,因此,需要自己实现ICB总线与AHB总线的通信,比较复杂。但是,通过阅读代码发现,其中,实现了ICB2AHBL模块,而我们的外设只有一个从机,一个主机,同时不涉及burst传输,因此,在功能上使用AHBL总线也可实现,因此,我们将AHB接口的外设通过修改部分控制信号与反馈信号之后,大胆的将其挂载在了ICB2AHBL总线下。以下是我们的实现过程。

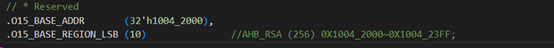

1.首先,我们在私有设备总线的例化模块中O15端口,为AHBL总线开辟了存储空间,通过系统存储映射实现,空间大小为1K(AHB总线接口的外设通常存储空间为1K)。如下图所示:

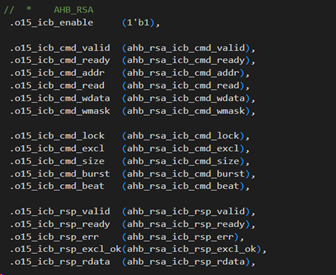

2.映射过存储空间后,我们将O15ICB总线使能,并将相关接口信号连接,如下图所示:

3.将ICB2AHBL总线例化,如下图所示:

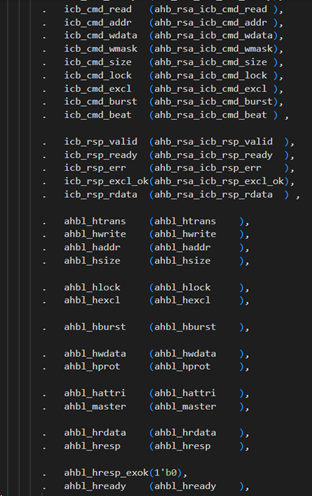

4.将AHB总线接口的外设例化,挂载在AHBL总线上:

从图中可以看到AHB总线相比AHBL总线接口信号有所不同,AHB总线可以实现一主多从或者一从多主的互联结构,因此需要仲裁进行选择并使能从机,因此,存在hsel信号表示从机的使能;此外AHB总线结构中还存在两个HREADY信号,即hready_in 与hready_out,其中,从机的hready_in信号一般置为高信号,表示一直响应。因此,ahb外设信号连接如上图所示。

至此,硬件代码添加完毕。之后便需要根据AHB接口的外设中定义的寄存器,配置软件相关代码。

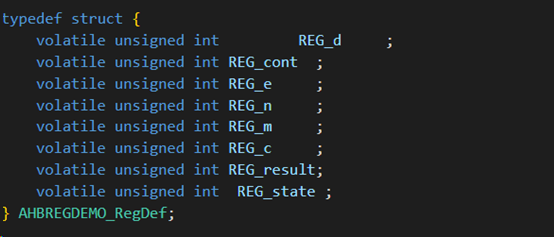

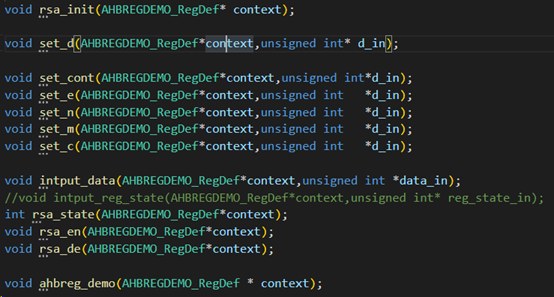

5.根据AHB的外设新建头文件,并进行相关寄存器结构体与函数的定义,如下图所示:

这里使用了结构体指针,方便操作结构体中的相关成员。

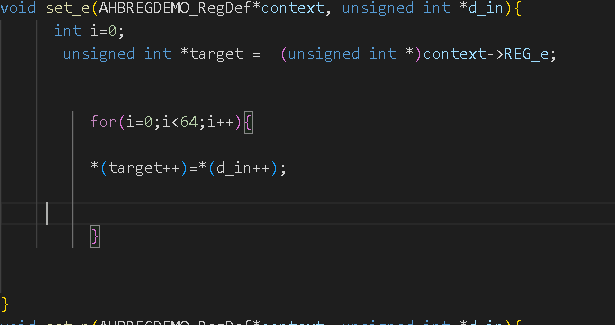

6.以set_e函数为例,展示了对结构体成员的操作,如下图所示:

通过使用,->符号便可指向相关结构体成员变量。

以上便是软件的配置,最后将软件代码进行编译,生成.Verilog文件,将文件相关路径加入到硬件仿真代码tb中,便可在仿真软件中进行仿真,验证是否正确添加,功能是否正确实现。