团队编号:CICC2400

团队名称:啊啊对对对队

首先将e203的源代码从网站上下载下来,网址如下。

https://github.com/riscv-mcu/e203_hbirdv2

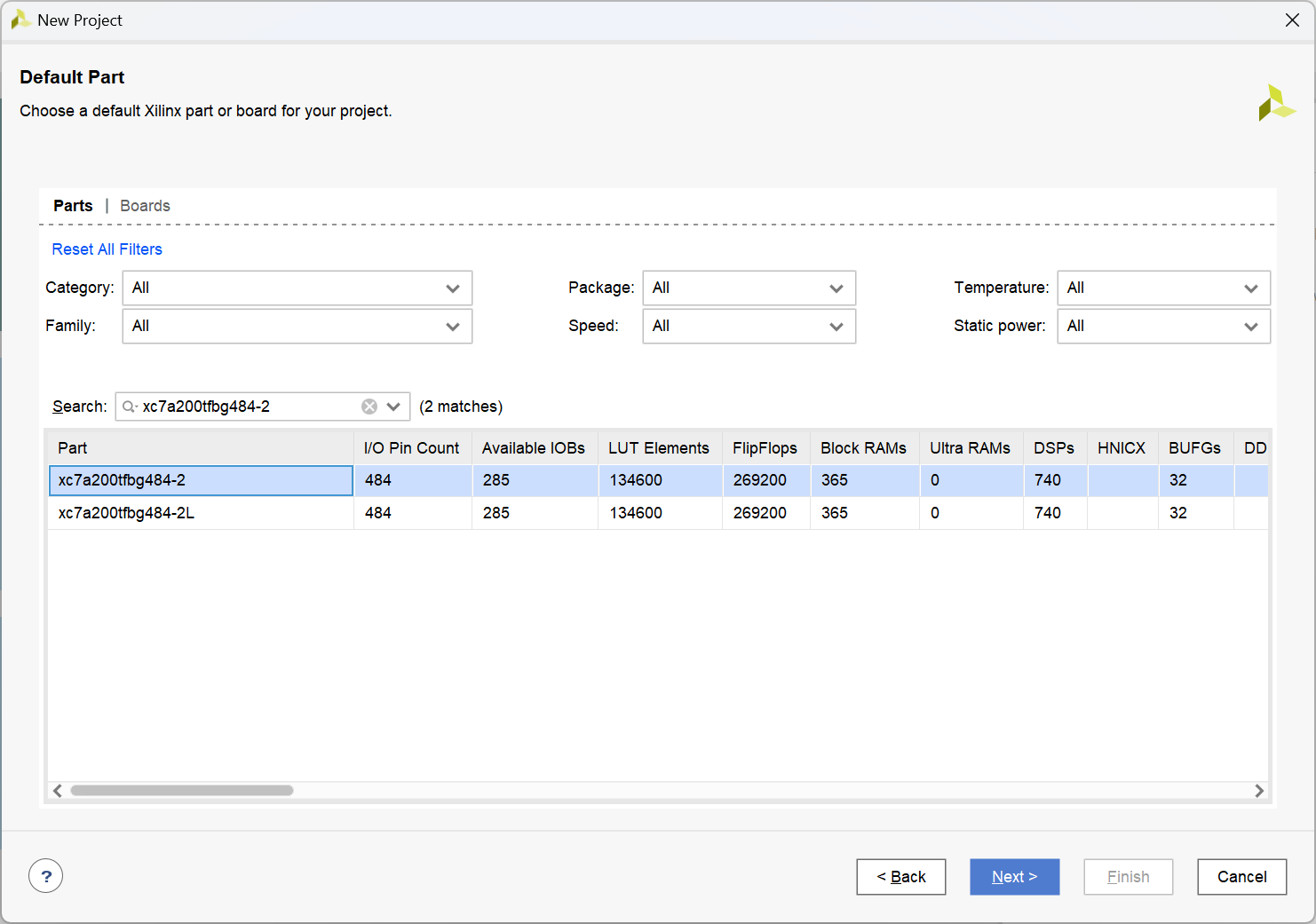

下载并解压文件,在Vivado中创建项目工程,要注意选择与自己的FPGA相匹配的芯片型号,这里作者所用开发板为DDR200T,因此选择xc7a200tfbgclg484-2。

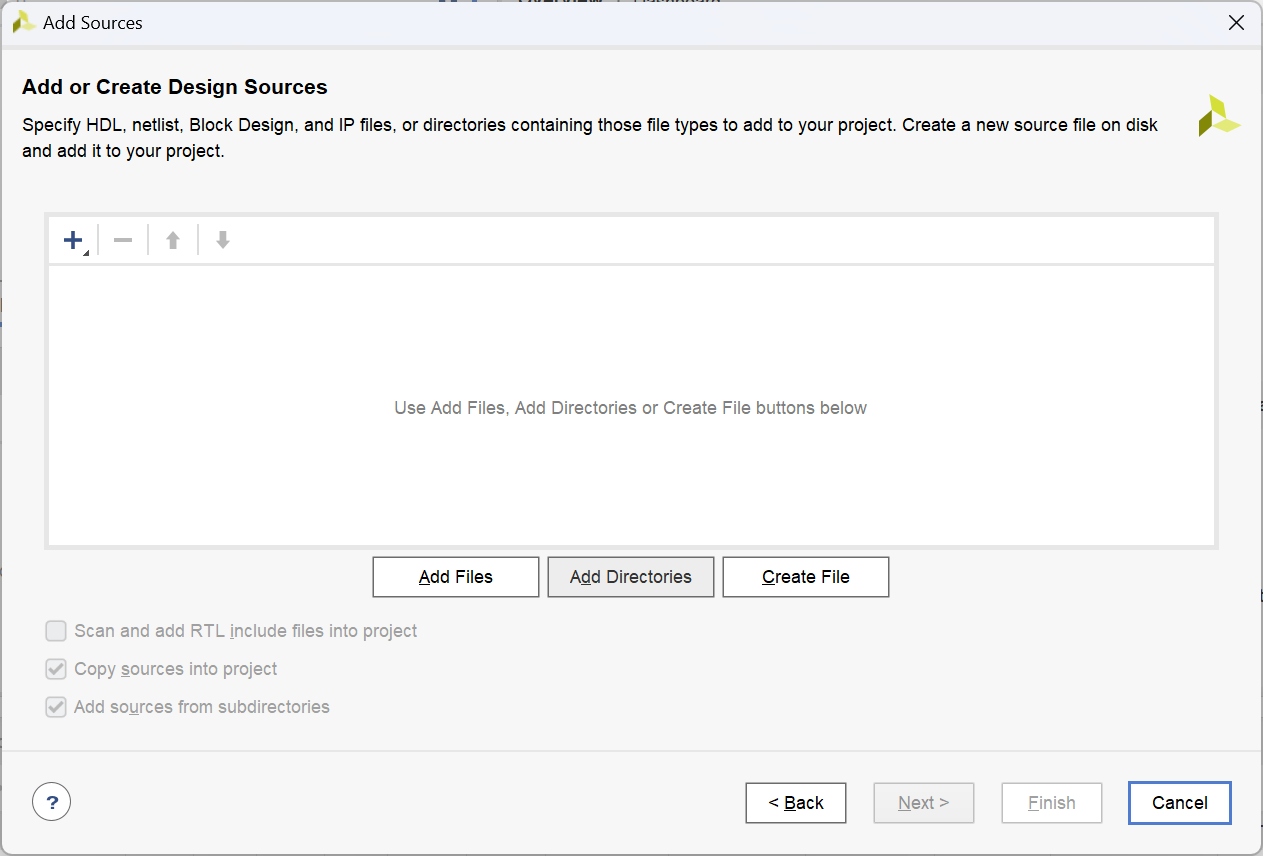

创建好工程后,在Add Sources选择Add design sources-Add Directories

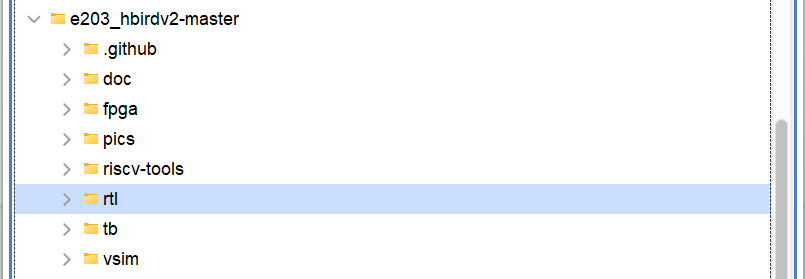

选择解压好的e203_hbirdv2-master文件夹中的rtl文件夹,添加所有RTL文件。同时添加e203_hbirdv2-master/fpga/ddr200t/src中的system.v

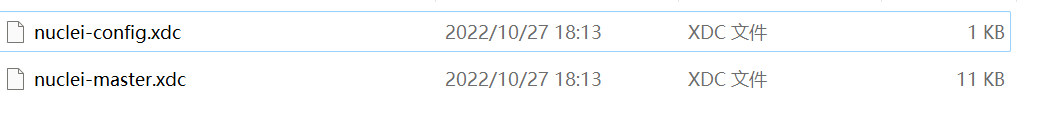

在Add Sources中选择添加constraints-Add Files,选中解压好的e203_hbirdv2-master/fpga/ddr200t/constrs文件夹中的全部两个文件,添加到项目的约束中去,这两个约束为DDR200T开发板所用约束,要想适配其他开发板,需要自行调整。

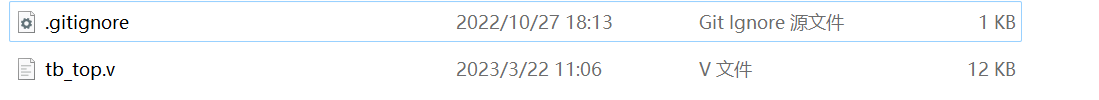

在Add Sources中选择添加simulation files,添加e203_hbirdv2-master/tb中的tb_top.v。

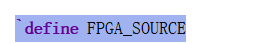

至此,所有文件已经添加完成,在config.v中添加定义FPGA_SOURCE,并将e203_defines.v设为verilog header与Global Include。

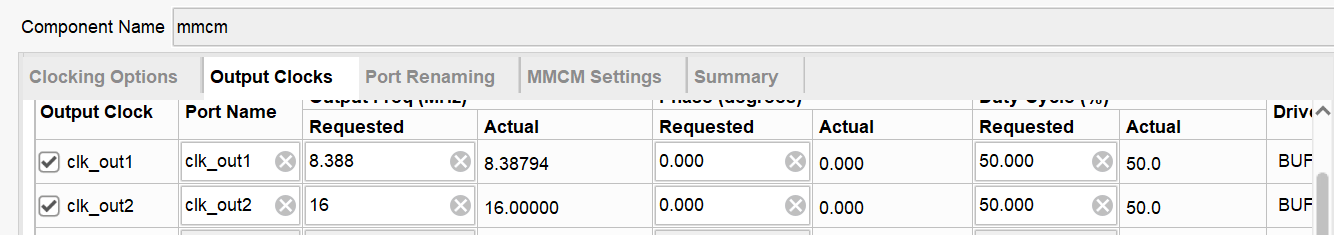

在IP Catalog中添加添加clocking_wizard,名称改为mmcm,在output界面中选择两个输出,分别为8.388MHz与16MHz.

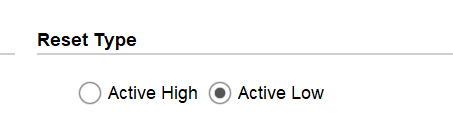

将Reset Type设为Active Low,点击OK,完成添加。

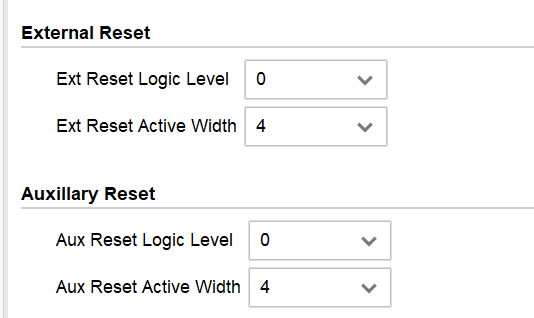

在IP Catalog中添加添加Processor system reset。名称改为reset_sys,将下图中的两个Level改为0,点击OK,完成添加。

将system.v设为顶层模块,至此,整个工程设置完毕,接下来可以进行,仿真、综合、实现等工作。