团队编号:CICC1649

团队名称:巴巴托斯

学校名称:重庆邮电大学

指导老师:孟杨,陈国平

团队成员:杨浩溢,赖小均,董川江

AXI GPIO简介

AXI-GPIO是一种Xilinx公司开发的外设IP,可以连接到AXI总线上,并提供GPIO(General Purpose Input Output)功能。AXI-GPIO主要有以下功能:

1.GPIO引脚控制:AXI-GPIO可以控制多个GPIO引脚的输入输出状态,每个GPIO引脚占用1个比特位。可以通过配置方向寄存器(Direction Register)来设置GPIO引脚的输入输出方向,通过配置数据寄存器(Data Register)来控制GPIO引脚的输出状态。

2.GPIO引脚读取:AXI-GPIO可以读取多个GPIO引脚的输入状态,每个GPIO引脚占用1个比特位。可以通过数据寄存器2(Data Register 2)来读取GPIO引脚的输入状态,数据寄存器仅用于写入GPIO引脚的输出状态。

3.GPIO中断控制:AXI-GPIO可以控制多个GPIO引脚的中断使能状态和中断触发模式。可以通过中断控制寄存器(Interrupt Enable Register)来使能或禁用GPIO引脚的中断,通过中断触发模式寄存器(Interrupt Type Register)来设置GPIO引脚的中断触发模式,例如上升沿触发或下降沿触发。

4.AXI接口支持:AXI-GPIO支持AXI总线协议,可以与其他AXI外设进行通信。可以通过AXI接口进行配置和控制,例如读写寄存器、设置中断等。

AXI-GPIO广泛应用于FPGA和SoC系统中,可以用于控制外部设备、实现状态检测、进行通信协议等。AXI-GPIO的灵活性和可靠性使其成为嵌入式系统开发中的重要外设IP。

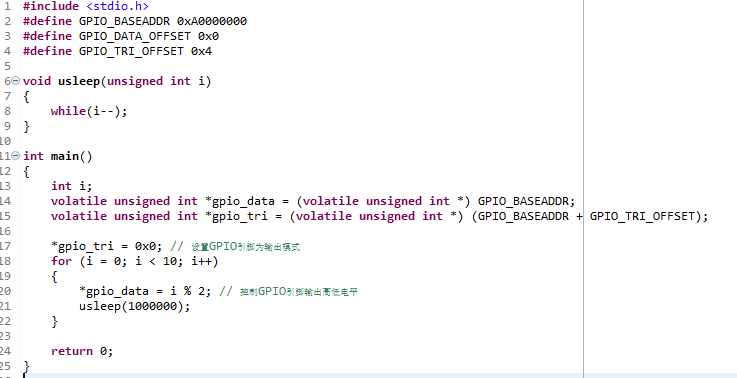

示例代码

这是一段简单的C语言代码,主要实现了对GPIO引脚的控制。首先定义了GPIO的基地址和偏移地址,然后通过指针访问GPIO的数据寄存器和方向寄存器,从而实现对GPIO引脚的控制。在主函数中,将GPIO引脚设置为输出模式,并循环控制GPIO引脚输出高低电平。每次输出后,延时一会,以便观察输出结果。最后返回0,表示程序执行成功。

注意事项

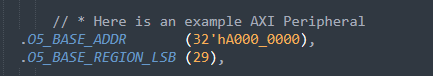

需要在e203_subsys_mems.v文件找到AXI4的地址

想要了解更多关于AXI GPIO的用法,参考PG144文档