队伍编号: CICC2071

添加浮点模块后,需要为处理器添加浮点状态寄存器。浮点寄存器记录了浮点和舍入模式,以及出现计算错误的异常。

fcsr寄存器可以用FRCSR和FSCSR指令读写,它们是构建在底层CSR访问指令之上的汇编伪指令。FRCSR通过将fcsr复制到整型寄存器rd来读取fcsr。fcsr通过将fcsr中的原始值复制到整型寄存器rd来交换fcsr中的值,然后将从整型寄存器rs1获得的新值写入fcsr。

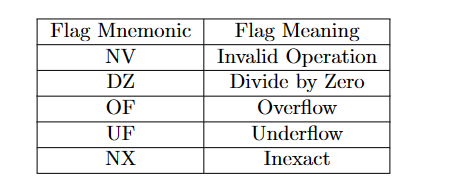

risc-v官方的fcsr配置如下图所示:

fcsr的第31-8位保留给其他标准扩展,包括十进制浮点数的“L”标准扩展。如果这些扩展不存在,实现将忽略对这些位的写入,并在读取时提供零值。标准软件应该保留这些字节的内容。

其中frm对应浮点的舍入模式,当指令中的rm值为111时,会读取该fcsr中的frm[7:5]值作为舍入模式。使用这种舍入方式一般称为动态舍入方式。即舍入方式可以通过软件方式更改fcsr值配置。

若指令中的rm值不为111则使用静态舍入模式,使用指令自带的舍入。

舍入模式关系图如下:

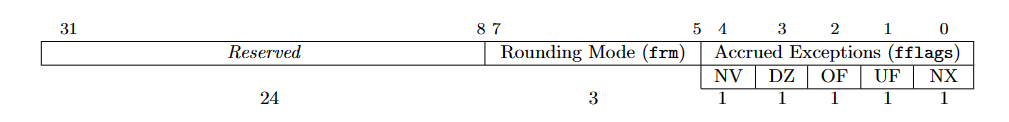

fscr的低5bit提供了计算异常位分别对应5种异常,无效操作,除零,上溢,下溢,不精确