1 队伍介绍

报名编号:CICC1981

团队名称:鼠队

团队成员:赵嗣纬,熊园园,林欣铨

部分积压缩是将多个部分积压缩成2个数并交由加法器产生最后结果。它既是一种加速乘法运算速度的普遍方法,又是乘法器性能的另一制约因素。

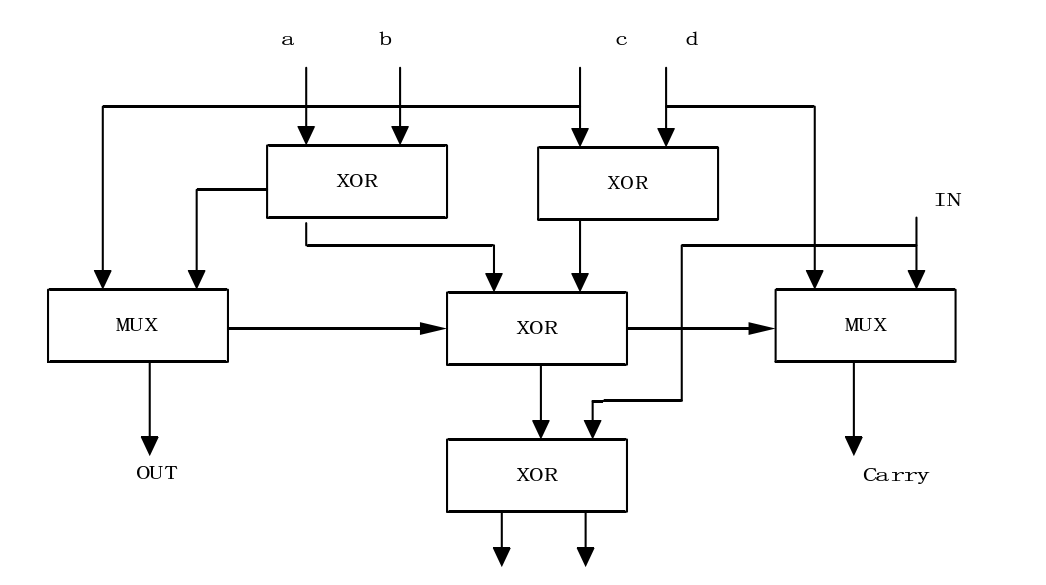

阵列乘法器中广泛使用进位保留加法器(CSA)。在进位保留加法器中,仅在最后一步才进行进位传播,而在其他步只是产生部分和与进位序列。这样进位保留加法器接收3个n位的操作数,产生2个n位的结果:一个n位的部分和与一个n位的进位。第2个CSA接收这2个结果和另一个输入的操作数,产生新的部分和与进位。

Wallace 树型压缩结构的核心是压缩器,核心是3-2进位保留加法器CSA( Carry Save Adder)。而传统的4-2压缩器是源于两个3-2CSA进行串联组合得到的,会有4个异或门的延迟。还有提出6-3压缩器,7-3压缩器和8-2压缩器都是这两种基础压缩器进行级联所得,这里不在赘述。3-2一位压缩器可以看成是一个一位全加器,4-2一位压缩器可以看作两个全加器的级联。另外多个3-2一位压缩器链式链接,多个4-2一位压缩器链式链接,才构成了在部分积中使用的压缩器。