喜欢0次

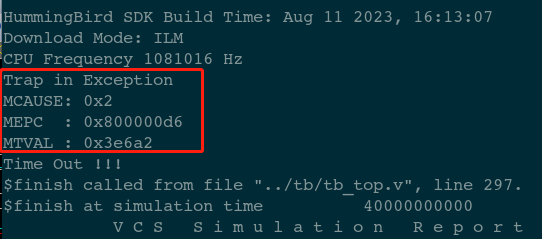

我们已经在内核中添加了浮点指令,测试用例也都能通过,但是使用IDE生成coremark仿真时会trap in exception:

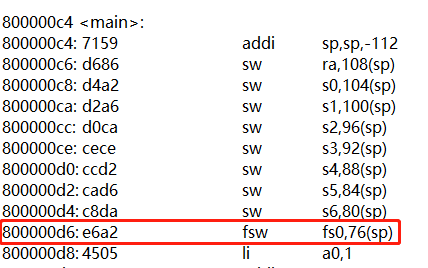

显示800000d6这个地址有问题。查看dump文件:

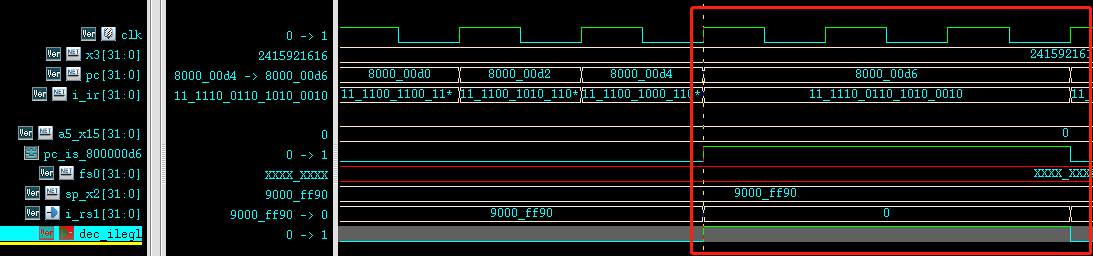

发现这是fsw指令,继续查看对应的波形:

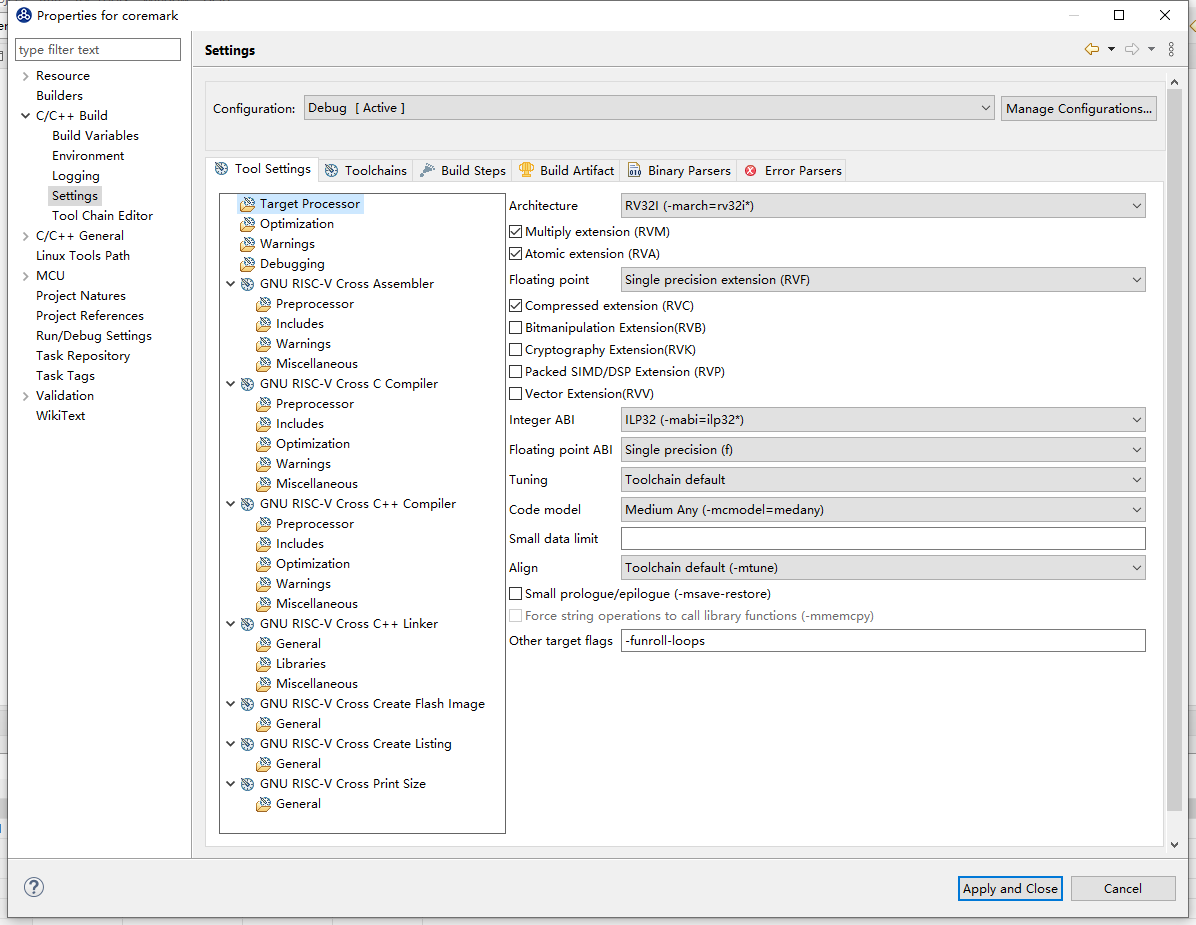

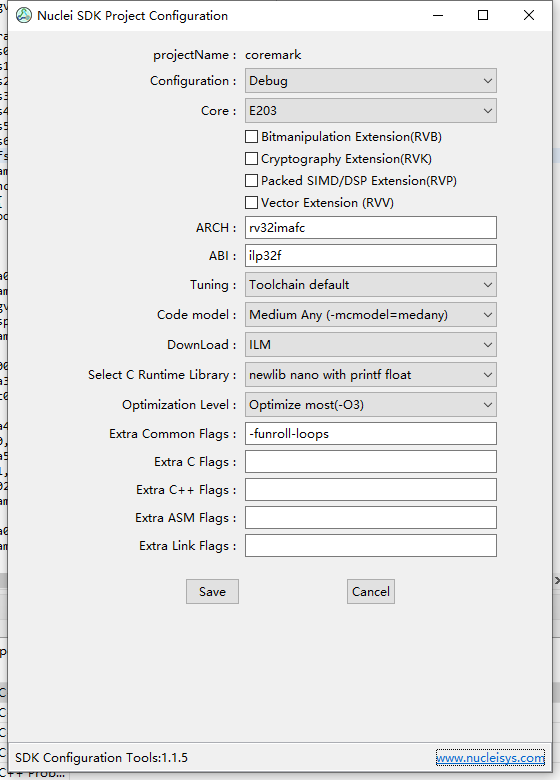

发现这条是非法指令,难道是生成.verilog文件的时候出错了吗?IDE用的是nuclei studio 202212,设置如下:

按照这个帖子的方法生成.verilog和.dump,https://www.riscv-mcu.com/community-topic-id-1286.html

build之后也没有error和warning,请问可能哪里出错了呢?