本队伍编号CICC3042,本篇文章介绍Hbirdv2移植到Nexys4 DDR(现已改名为Nexys A7-100T)和Nexys Video开发板,开发板链接:

Nexys A7-100T:

http://www.digilent.com.cn/products/product-nexys-4-ddr-artix-7-fpga-trainer-board.html

Nexys Video:

http://www.digilent.com.cn/products/product-nexys-video-artix-7-fpga-trainer-board-for-multimedia-applications.html

Hbirdv2对于不同开发板的移植步骤基本相同,可以直接新建Vivado工程,也可以在官方提供的ddr200t和mcu200t相应的脚本基础上修改,主要包括以下几步:

1. 添加源文件

2. 添加时钟

3. 修改system.v,留下需要的顶层接口

在步骤1中,准备好Hbirdv2的源文件,可以在Vivado添加源文件时直接导入e203_hbirdv2项目中的rtl文件夹。

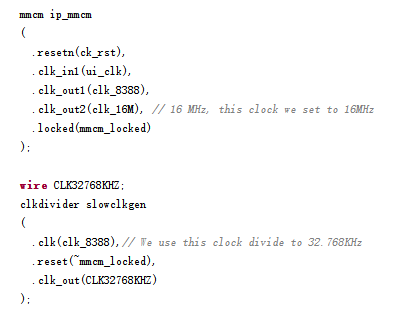

在步骤2中,我们需要生成两个时钟,16MHz时钟作为处理器时钟,32.768KHz时钟为常开域时钟。参考蜂鸟v1中Hbirdv1在Arty开发板上的移植,通过clocking wizard IP核生成两个时钟,clk_16M即为16MHz信号,clk_8388为8.388KHz信号,通过clkdivider模块256分频后得到近似的32.768KHz时钟。其他板子比如Genesys2的时钟源为差分输入,同样使用clocking wizard IP核来配置。

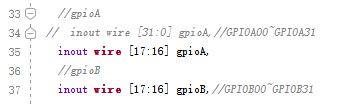

在步骤3中,我们需要修改顶层接口等内容,比如去掉不需要的接口,添加访问DDR接口等。在我们的项目中暂时只需要两个uart接口,即GPIO的16、17位,为了避免在约束文件中分配过多接口,将system.v中的顶层接口中的GPIO修改为以下内容:

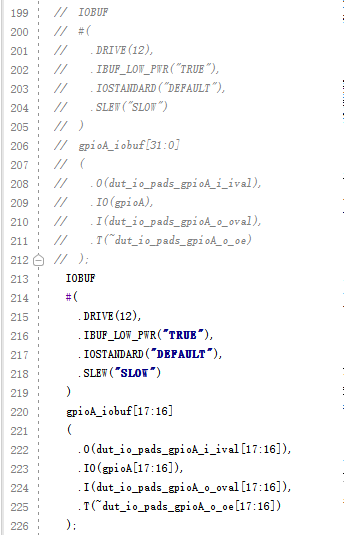

同样地,对后面的IOBUF模块进行修改:

注意在Nexys4 DDR和Nexys Video开发板中需要通过STARTUPE2原语来驱动Quad SPI flash,而在Arty开发板中不需要。因此这里的qspi0_sck不需要接出,在顶层接口中注释掉,并例化STARTUPE2模块:

STARTUPE2

#(

.PROG_USR("FALSE"),

.SIM_CCLK_FREQ(0.0)

)

STARTUPE2_inst

(

.CFGCLK (),

.CFGMCLK (),

.EOS (),

.PREQ (),

.CLK (1'b0),

.GSR (1'b0),

.GTS (1'b0),

.KEYCLEARB (1'b0),

.PACK (1'b0),

.USRCCLKO (qspi0_sck), // First three cycles after config ignored, see AR# 52626

.USRCCLKTS (1'b0), // 0 to enable CCLK output

.USRDONEO (1'b1), // Shouldn't matter if tristate is high, but generates a warning if tied low.

.USRDONETS (1'b1) // 1 to tristate DONE output

);

在步骤4中修改约束文件,这里以Nexys Video为例,首先分配时钟引脚,将pmu_paden和pmu_padrst连接到LED,将mcu_wakeup连接到button,将fpga_rst连接到板子上的reset按键,注意这里的普通按键按下是高电平,而reset按键按下是低电平。随后分配JTAG 接口和qspi接口。注意qspi0_sck连到了STARTUPE2模块上,不要写到约束文件中:

set_property -dict { PACKAGE_PIN T19 IOSTANDARD LVCMOS33 } [get_ports { qspi0_cs }]; #IO_L6P_T0_FCS_B_14 Sch=qspi_cs

set_property -dict { PACKAGE_PIN P22 IOSTANDARD LVCMOS33 } [get_ports { qspi0_dq[0] }]; #IO_L1P_T0_D00_MOSI_14 Sch=qspi_dq[0]

set_property -dict { PACKAGE_PIN R22 IOSTANDARD LVCMOS33 } [get_ports { qspi0_dq[1] }]; #IO_L1N_T0_D01_DIN_14 Sch=qspi_dq[1]

set_property -dict { PACKAGE_PIN P21 IOSTANDARD LVCMOS33 } [get_ports { qspi0_dq[2] }]; #IO_L2P_T0_D02_14 Sch=qspi_dq[2]

set_property -dict { PACKAGE_PIN R21 IOSTANDARD LVCMOS33 } [get_ports { qspi0_dq[3] }]; #IO_L2N_T0_D03_14 Sch=qspi_dq[3]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

使用STARTUPE2原语驱动qspi flash后,在实际下载程序到flash过程中发现Nexys4 DDR可以正常运行,而Nexys Video无法正常运行,调试发现flash地址空间中只有前几条指令正常,其他指令和反汇编文件对不上或者全是0,这里是不是板子的原因有待深入研究。下载到ilm中都可以正常运行。

下一篇分享在windows/linux下使用Olimex和蜂鸟调试器下载程序。