一、 队伍介绍

本参赛队队名为“Supernova”,报名编号:CICC2796。本篇为蜂鸟E203系列分享第一篇。本篇介绍的内容是Hbirdv2在vivado2018.3上的仿真工作。

二、 前言

仿真前,我们首先需要获得仿真需要的.verilog文件,我们可以在官方给的文件中获得实例.verilog文件,如果我们想要仿真自己C程序编译出来的对应.verilog文件,我们则需要先生成此文件。

三、 仿真流程

1、

首先需注释掉源码中的一些断言部分,此部分不做介绍。

2、

生成我们需要的.verilog文件。

方法一:在ubuntu18.04中配置好SDK,具体配置可以参考《手把手教你设计CPU----RISC-V处理器》或《RISC-V架构与嵌入式开发快速入门》一书,也可在网上找寻相关资料,配置好SDK后,我们可以自行编写C程序和makefile文件,在hbird-e-sdk路径下输入命令make dasm PROGRAM=test3 BOARD=hbird-e200 CORE=e203 DOWNLOAD=itcm USE_NANO=1 NANO_PFLOAT=0(注意:DOWNLOAD=itcm必须改为itcm,因为在vivado中仿真时我们是将程序放在itcm中的,程序一开始要在这里加载)

最终我们可以在hbird-e-sdk/software/下对应的项目文件夹下生成可执行文件、.verilog文件、.dump文件。

方法二:使用芯莱的NucleiStudio IDE,想要获得.verilog文件,我们需要选择当前项目的properties->C/C++

Build->Settings->Build Steps->Post-build

steps 增加如下命令:

riscv-nuclei-elf-objcopy -O verilog "${BuildArtifactFileBaseName}.elf" "${BuildArtifactFileBaseName}.verilog";sed -i 's/@800/@000/g' "${BuildArtifactFileBaseName}.verilog"; sed -i 's/@00002FB8/@00002000/g' "${BuildArtifactFileBaseName}.verilog";

最终可以在debug目录下找到相应的.verilog文件(注意:同样的project settings的DOWNLOAD选项不要选择FLASH,要选ILM)

具体方法可以参考论坛中的分享贴,写的十分详细https://www.rvmcu.com/community-topic-id-386.html

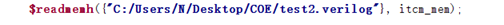

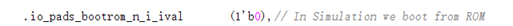

3、 将tb_top文件中的readmemh函数所读取的文件改为上一步生成的.verilog文件;将tb_top文件中对于顶层模块实例化的io_pads_bootrom_n_i_ival信号置为0(核从itcm中加载程序)。

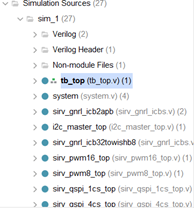

4、 将源码中的tb_top设置为顶层文件并进行仿真

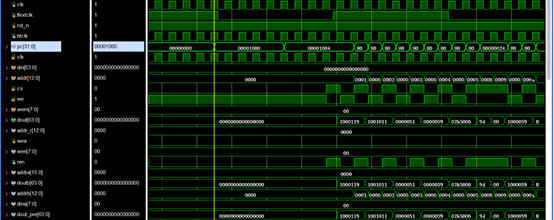

5、 观察波形,检查其结果是否与预期一致

四、 总结

本次分享主要是对在vivado中对蜂鸟E203行为级仿真时所遇到的一些问题进行介绍与分享。