主办单位:

中国电子学会

承办单位:

东南大学

南京市江北新区管理委员会

协办单位:

示范性微电子学院产学融合发展联盟

江苏省产业技术研究院专用集成电路技术研究所

南京江北新区产业技术研创园

支持单位:

新思科技

Cadence

Mentor

华大九天

芯来科技

南京集成电路产业服务中心(ICisC)

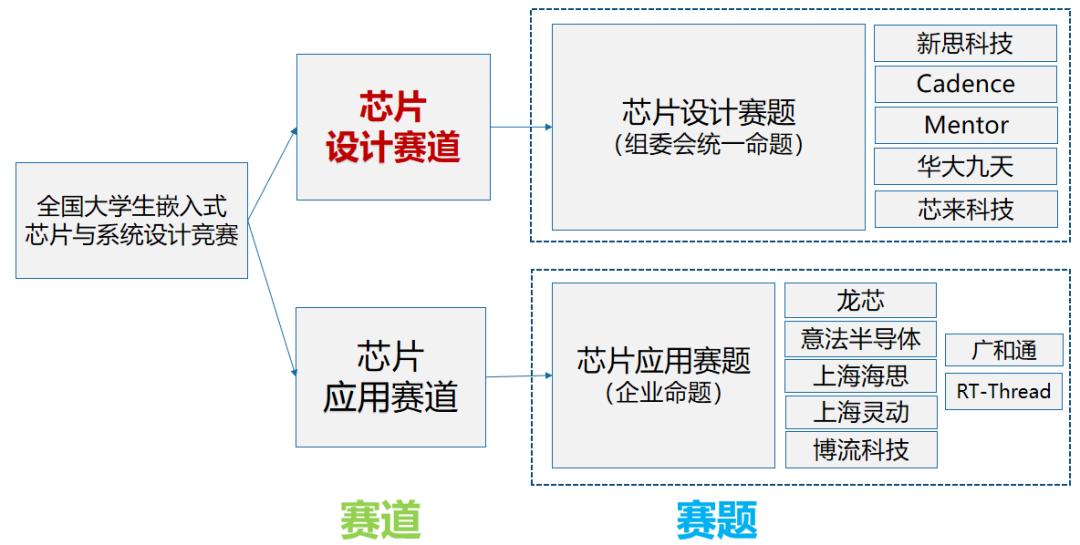

(本竞赛还有芯片应用赛道,欢迎关注报名!)

芯片设计赛道:本赛道基于组委会指定的芯片硬件框架下,以特定应用场景,由参赛队自主选题的模式,完成相关芯片的设计与验证,达到可提交签核的标准。(2021年赛题完成指定工艺库的综合网表实现即可) 详见竞赛选题指南(请看下文链接)。

1、赛道特色:

以芯片TapeOut为目标的芯片设计大赛

2、企业需求与真实工艺库:

(1)赛题与真实项目的零距离接触

(2)集成电路企业面试直通车

3、评选原则:

创意实现、接近产品、市场价值

大赛报名时间:2021年4月1日-2021年5月31日

作品设计时间:2021年5月- 9月

作品提交时间:2021年9月18日18点前

初赛评审时间:2021年9月19日

分赛区复赛时间:2021年9月下旬

本届竞赛分初赛、分赛区复赛及全国总决赛三阶段进行。

登录竞赛官网(www.socchina.net)注册报名。经专家组评定确定是否获得后续资格。

每参赛队由不多于3名学生组成,可有不超过2名指导老师。

根据参赛学生学历层次,竞赛分:①本科组、②研究生组。

全体成员为本科生的参赛队为本科组;参赛队员中只要有一名研究生即为研究生组;高职高专队伍统一纳入本科生组评比;参赛队员身份以报名截止日提交身份为准。

赛题简介

本赛题要求参赛队面向低功耗智能识别应用(包括但不限于:图像识别、视频识别、语音识别、图形识别、动作识别等),进行核心IP模块的硬件设计,并基于组委会指定的芯片硬件框架:

完成集成该IP的系统搭建与功能验证;

完成基于指定工艺库的综合和评估。

芯片硬件框架

( 蓝色部分,提供参考设计)

本赛题,组委会指定的硬件框架如上图所示,包括:

RISC-V MCU以及相关的软件开发套件(或其它同类RISC MCU、参赛队自主设计的系统控制器模块等)

AMBA2.0 AHB/APB总线(或其它同类嵌入式系统总线模块、参赛队自主设计的系统互联模块)

中断控制器

基于Memory Compiler的SRAM存储模块(位宽、深度、个数可根据实际需求定制,但位宽不得超过1024bits,总大小不得超过500Kbytes)

UART模块,Timer模块,I2S模块,以及GPIO模块

参赛队需要基于上述硬件框架,完成面向目标应用的芯片系统设计与实现,包括:

首先,完成面向目标应用的核心功能IP模块设计与实现;

其次,使用指定硬件框架中的若干模块(一个或多个模块)、以及所设计的核心功能IP模块,完成芯片系统的搭建;

最后,基于所实现的芯片系统,完成功能仿真和电路综合。

面向低功耗智能识别的IP设计与应用系统开发(简称:嵌入式系统芯片设计)

——赛题方向:智能识别芯片设计

本赛题的主要需求(包括但不限于):

面向群体:研究生

基于组委会指定的芯片硬件框架,开发面向“智能识别”应用的核心IP硬件、以及集成该IP的系统。

指定的芯片硬件框架包括以下一个或多个模块:RISC-V MCU以及相关的软件开发套件(或其它同类RISC MCU、参赛队自主设计的系统控制器模块等)、AMBA2.0 AHB/APB总线(或其它同类嵌入式系统总线模块、参赛队自主设计的系统互联模块)、中断控制器、基于Memory Compiler的SRAM存储模块(位宽、深度、个数可根据实际需求定制,但位宽不得超过1024bits,总大小不得超过500Kbytes)、UART模块,Timer模块,I2S模块,GPIO模块。

智能识别应用包括但不限于:图像识别、图形识别、视频识别、语音识别、动作识别等。

对于所选择的智能识别应用,其测试库需为开源数据库,或者可以第三方获取并独立验证的数据库。

需完成面向智能识别应用的核心IP设计,需要完成目标应用的核心功能:IP设计文档、算法或功能验证模型、基于HDL(推荐Verilog)的RTL功能模型、基于指定工艺库的综合网表Netlist、综合后的时序/资源/功耗等参数报告与分析。

需基于指定的芯片硬件框架,完成集成5)所设计IP的智能识别应用系统开发,包括:RTL功能模型、基于指定工艺库的综合网表Netlist、综合后的时序/资源/功耗等参数报告与分析。

上述完成的IP设计和系统开发,需结合实际的应用场景,对硬件系统架构和IP电路设计方案,进行分析和评估,在以下一个或多个指标上进行优化设计,包括但不限于:性能、功耗、能效、吞吐率、识别精度、场景适配能力、系统灵活性等。

组委会鼓励方向(完成以下方向,组委会额外着重考虑):

方向1:完成上述6)所开发系统的FPGA功能验证,并具有一定的可展示性。方向2:完成上述6)所开发系统的P&R以及Layout设计,并进行后仿验证和评估。方向3:采用国产EDA工具,完成上述5)IP模块或上述6)系统开发中的部分设计仿真、综合评估等工作。面向群体:本科生

赛题要求与研究生组基本相同,不同点在于:

可以选择相对简单的智能识别应用,例如:手写数字识别等;

研究生组赛题要求中的第7小项(结合实际应用场景的性能/功耗等设计指标优化评估),不作为必选要求。

本芯片设计赛道,会安排相关培训与指导,请关注竞赛官网、竞赛公众号、芯片设计赛道QQ群。

联系方式

芯片设计赛道QQ群

264443932

陈老师 18600043989 chenjunyan@icisc.cn

汪老师 13901584204 wangchen1@icisc.cn

嵌入式大赛

官方网站

http://www.socchina.net/

官方QQ群

575699069

作为中国大陆首家纯本土专业RISC-V处理器IP和芯片解决方案公司,芯来科技致力于RISC-V处理器IP开发及商业化。自2018年成立以来,凝聚了一支本土经验丰富的处理器研发团队。从零开始全自主研发,相继推出了N100、N200、N300、N/NX/UX600、N/NX/UX900等系列产品覆盖了从低功耗到高性能的各种场景需求。芯来的处理器IP已授权众多知名芯片公司进行量产,实测结果达到业界一流指标。

聚焦RISC-V处理器内核研发,致力于赋能本土产业生态,是芯来科技贯彻始终的愿景与追求。

更多详情访问:www.nucleisys.com

▼往期精彩回顾▼

芯来科技将出席“南京RISC-V生态与应用技术研讨会”

芯来科技RISC-V处理器支持鸿蒙LiteOS-M内核

*免责声明:以上内容仅供交和流学习之用。如有任何疑问或异议,请留言与我们联系。