团队名称:Great Bee

大家好,本团队此次分享的内容为时钟移相电路加速模块的设计。

数据接收时由于传感器输出的LVDS信号,即低压差分信号,LVDS信号是利用一个低压差分对的相对关系来表示信号的高低,电压约为350mV左右。为了将差分信号转换成单端信号的形式,设计中加入了Xilinx公司解决差分输入的原语IBUFGS,直接在接收端例化一个接口逻辑门,可将LVDS信号转换成单端信号。之后考虑是数据对齐的问题,由于传感器的数据信号和时钟信号是同步跳变的,如果不加处理直接传入到FPGA引脚中,在基于逻辑的边沿变化采集时并不能对准数据稳定的时刻,而不能正确采集到数据。为了在时钟跳变时能对准数据的稳定时刻,通常在设计时可以采用以下方法:专用IP核延迟、锁相环移相和门电路延迟。逻辑门电路延迟是一种简单通用的方法,但是利用逻辑门作延时的缺点是单个逻辑门的时延微乎其微,若需要一定的延时往往需要大量的逻辑门串联的形式,信号的驱动能力减弱,也浪费了系统资源。设计中采用了锁相环的形式,利用Xilinx公司提供的时钟管理模块作为时钟移相,此模块的全称为Clocking Wizard,在定制模块时可以设置输入输出时钟、相移、占空比等信息,这里设置输入输出时钟均为120MHz,相移为90°,输入时钟移相电路加速模块。

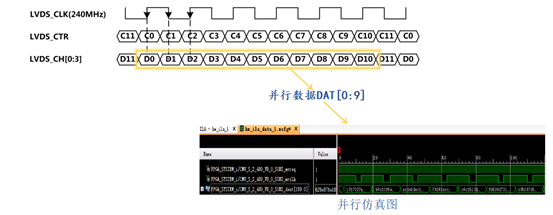

得到对齐的数据后,我们就要考虑将串行数据并行化的问题,传感器的ADC模式是10bits模式,代表一个像素10比特,控制信号也为10比特,采用合适的分频方式对数据进行采集并拼接即可得到并行数据。

在数据拼接时,10bits串行数据会并行成10bits并行数据,是一个像素的信息,16通道会同时产生16个并行数据,共160bits数据,将整个160bits数据并行起来传送到预处理模块中以便数据拼接成整行的形式。