在扩展指令时我们常常需要一些手段来帮助我们判断指令是否能够成功运行、运行状态是否正确。一方面,我们可以通过模拟器来实现,另一方面,在没有模拟器的情况下,我们可以通过将所扩展指令的二进制代码导入vivado仿真运行判断状态是否正确。

获取二进制代码

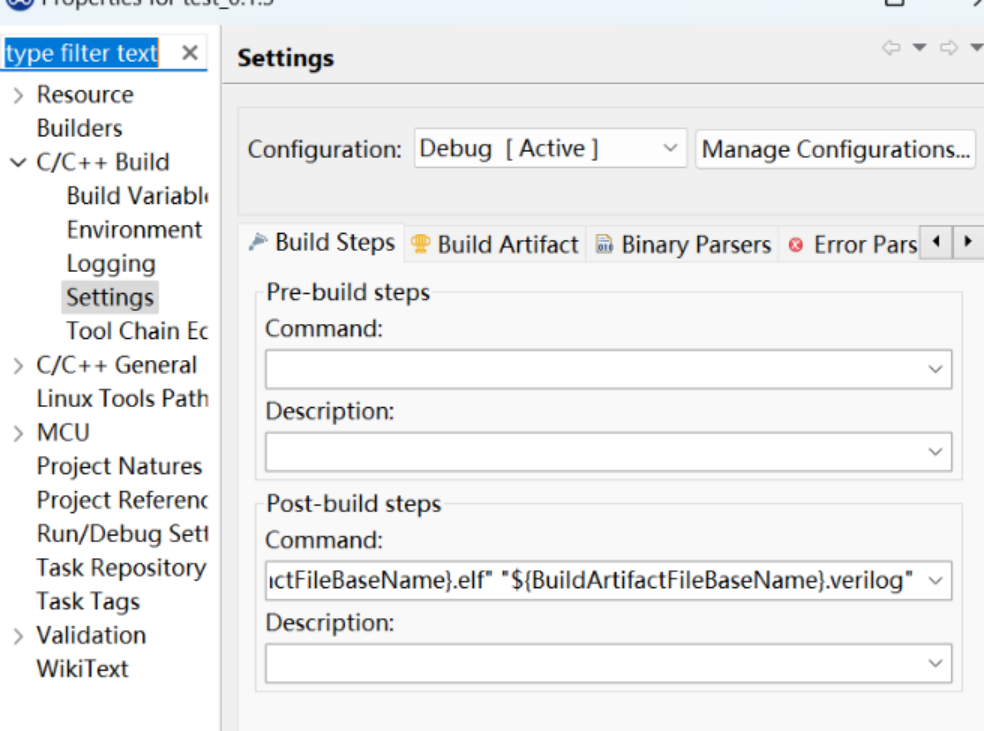

在Nucleistudio中打开相关项目的Properties,按路径打开C/C++ Build ->setting,找到Build Steps 选项并在Post-build Steps下添加指令

riscv-nuclei-elf-objcopy -O verilog "${BuildArtifactFileBaseName}.elf" "${BuildArtifactFileBaseName}.verilog"

应用后,点击build,会在project的路径下Debug中看到对应生成的.verilog文件。

同样的,加入

riscv-nuclei-elf-objdump -d "${BuildArtifactFileBaseName}.elf" > "${BuildArtifactFileBaseName}.dasm"

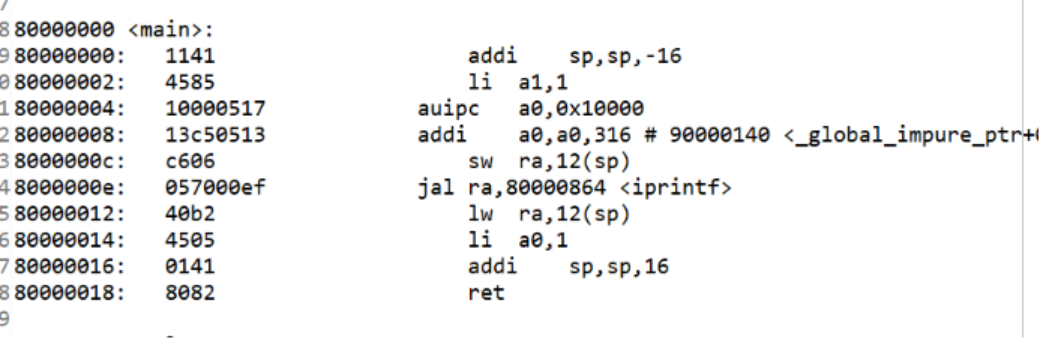

后build会生成对应的.dasm文件,用于查看对应的汇编指令。

获取测试指令

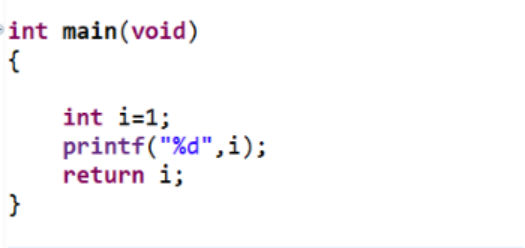

以helloworld为例,在生成对应的两个文件之后,我们可以选取想要测试的指令导入vivado

我们以测试

li a0 8

addi a0 a0 -8

为例

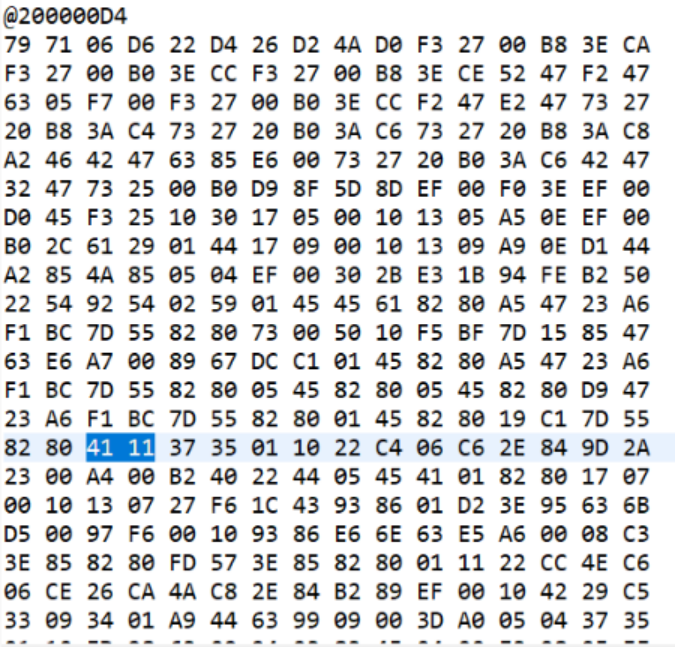

获取相应的二进制码将其转换为16进制导入vivado,方法就是将代码文件修改为.verilog文件并存入蜂鸟的tb文件夹,在vivado的tb中修改测试用例路径即可进行仿真。

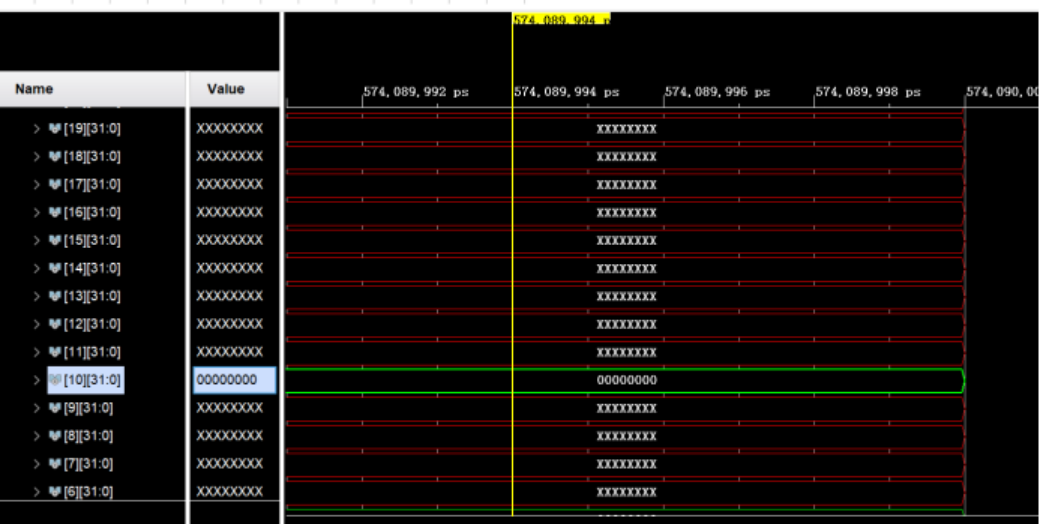

得到结果

A0值为0,说明指令正确读取并运行

通过这种方法我们可以在没有模拟器的情况下对自己扩展的指令进行测试,虽然略显复杂,但是在加深对代码理解的基础上还可以保证代码质量。