报名编号:CICC2353

称团队名:不划水队

所选杯赛:芯来RISC-V杯

乘法器的优化实现一般从两个方面入手。第一是减少生成的部分积数量,另外就是减少部分积累加的延时。

在开源的E203源码中,32*32乘法器是利用radix-4 booth编码产生部分积,每个周期做一次部分积的累加,加法(或者减法)操作使用ALU的加法器完成,尽可能减小内核面积。由于需要支持RV32M中的4条乘法指令(mul,mulh,mulhu,mulhsu),因此根据指令将操作数进行了两bit符号位扩展,34bit的乘数经过booth4编码后会生成17个部分积,因此一条乘法指令需要17个周期执行完成(不考虑back-to-back情况),最后根据指令输出32bit的结果。

我们将源码中迭代实现的乘法器改成了单周期乘法器实现。利用booth4编码产生17个部分积,经过6级CSA被压缩成两个部分积,最后使用RCA加法器得到最后的乘积。

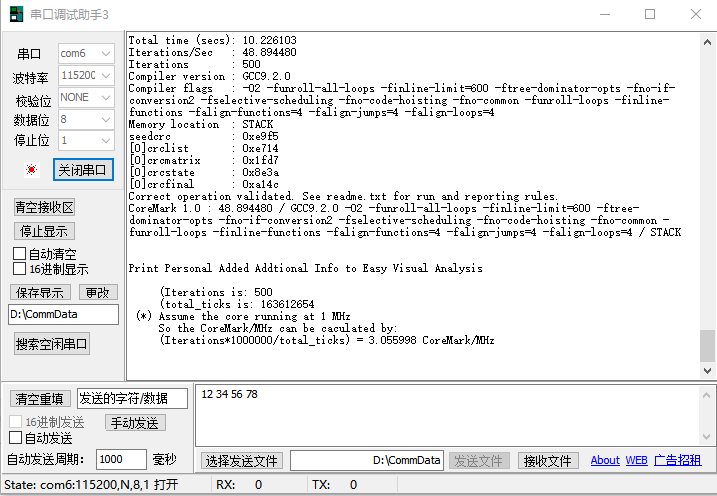

利用Coremark跑分结果如下:

往期分享:

【1】蜂鸟E203协处理器EAI指令及接口_全国大学生集成电路创新创业大赛_RISC-V论坛讨论_RISC-V MCU中文社区 (rvmcu.com)

【2】加密算法的应用_全国大学生集成电路创新创业大赛_RISC-V论坛讨论_RISC-V MCU中文社区 (rvmcu.com)

【3】国密系列算法简介及SM4算法原理介绍_全国大学生集成电路创新创业大赛_RISC-V论坛讨论_RISC-V MCU中文社区 (rvmcu.com)

【4】Demo_NICE软件源码解读及应用_全国大学生集成电路创新创业大赛_RISC-V论坛讨论_RISC-V MCU中文社区 (riscv-mcu.com)

【5】AES加密流程_全国大学生集成电路创新创业大赛_RISC-V论坛讨论_RISC-V MCU中文社区 (riscv-mcu.com)

【6】AES和SM4算法的可重构分析_全国大学生集成电路创新创业大赛_RISC-V论坛讨论_RISC-V MCU中文社区 (riscv-mcu.com)

【8】 AES加密流程_全国大学生集成电路创新创业大赛_RISC-V论坛讨论_RISC-V MCU中文社区 (riscv-mcu.com)